Answered step by step

Verified Expert Solution

Question

1 Approved Answer

COE 3 4 1 Department of Computer Science and Engineering Summer 2 0 2 4 Question 3 ( 2 0 % ) - Consider the

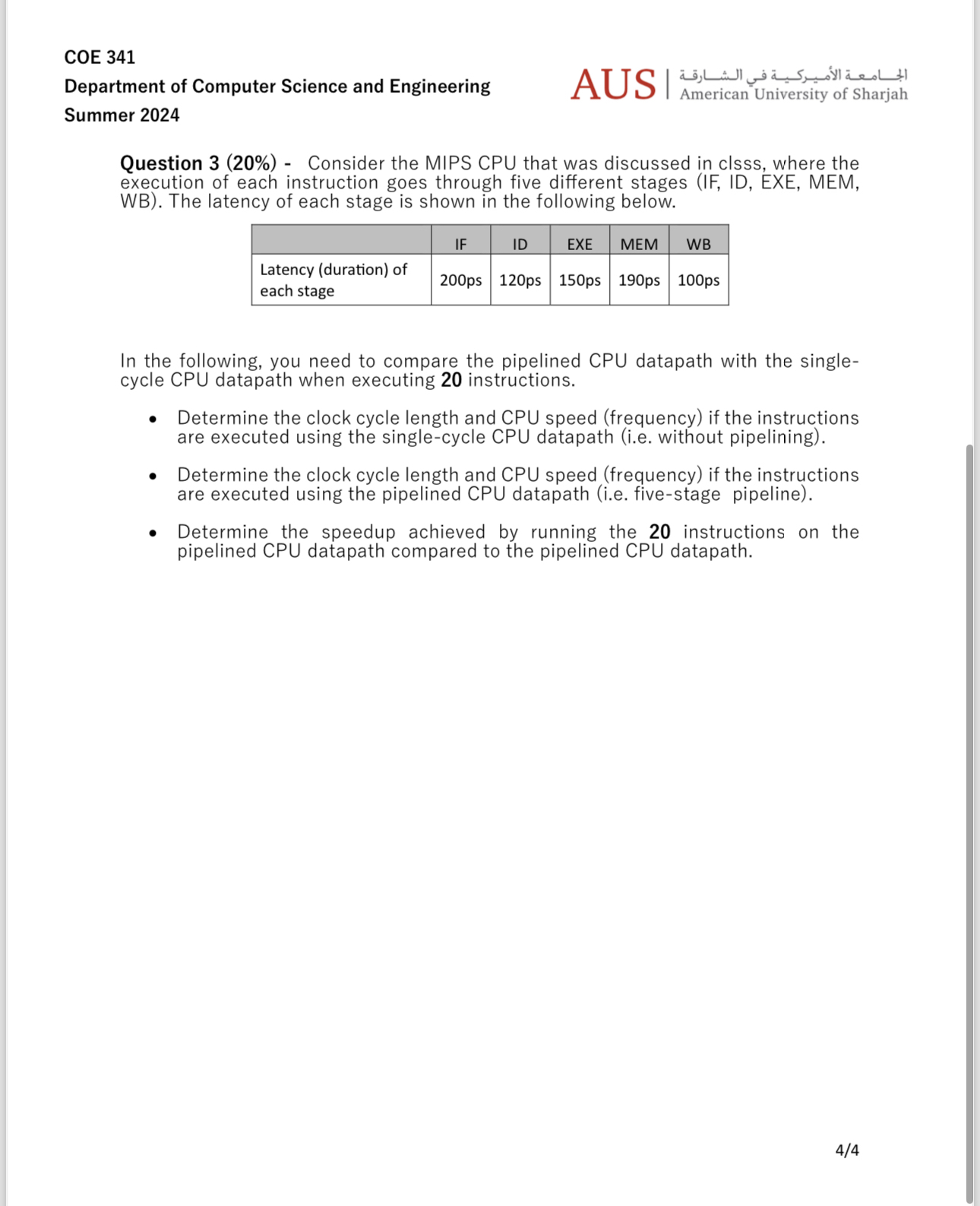

COE Department of Computer Science and Engineering Summer Question Consider the MIPS CPU that was discussed in clsss where the execution of each instruction goes through five different stages IF ID EXE, MEM, WB The latency of each stage is shown in the following below. tableIFIDEXE,MEM,WBtableLatency duration ofeach stage ps ps ps ps ps In the following, you need to compare the pipelined CPU datapath with the singlecycle CPU datapath when executing instructions. Determine the clock cycle length and CPU speed frequency if the instructions are executed using the singlecycle CPU datapath ie without pipelining Determine the clock cycle length and CPU speed frequency if the instructions are executed using the pipelined CPU datapath ie fivestage pipeline Determine the speedup achieved by running the instructions on the pipelined CPU datapath compared to the pipelined CPU datapath.

COE

Department of Computer Science and Engineering

Summer

Question Consider the MIPS CPU that was discussed in clsss where the execution of each instruction goes through five different stages IF ID EXE, MEM, WB The latency of each stage is shown in the following below.

tableIFIDEXE,MEM,WBtableLatency duration ofeach stage ps ps ps ps ps

In the following, you need to compare the pipelined CPU datapath with the singlecycle CPU datapath when executing instructions.

Determine the clock cycle length and CPU speed frequency if the instructions are executed using the singlecycle CPU datapath ie without pipelining

Determine the clock cycle length and CPU speed frequency if the instructions are executed using the pipelined CPU datapath ie fivestage pipeline

Determine the speedup achieved by running the instructions on the pipelined CPU datapath compared to the pipelined CPU datapath.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started