Question

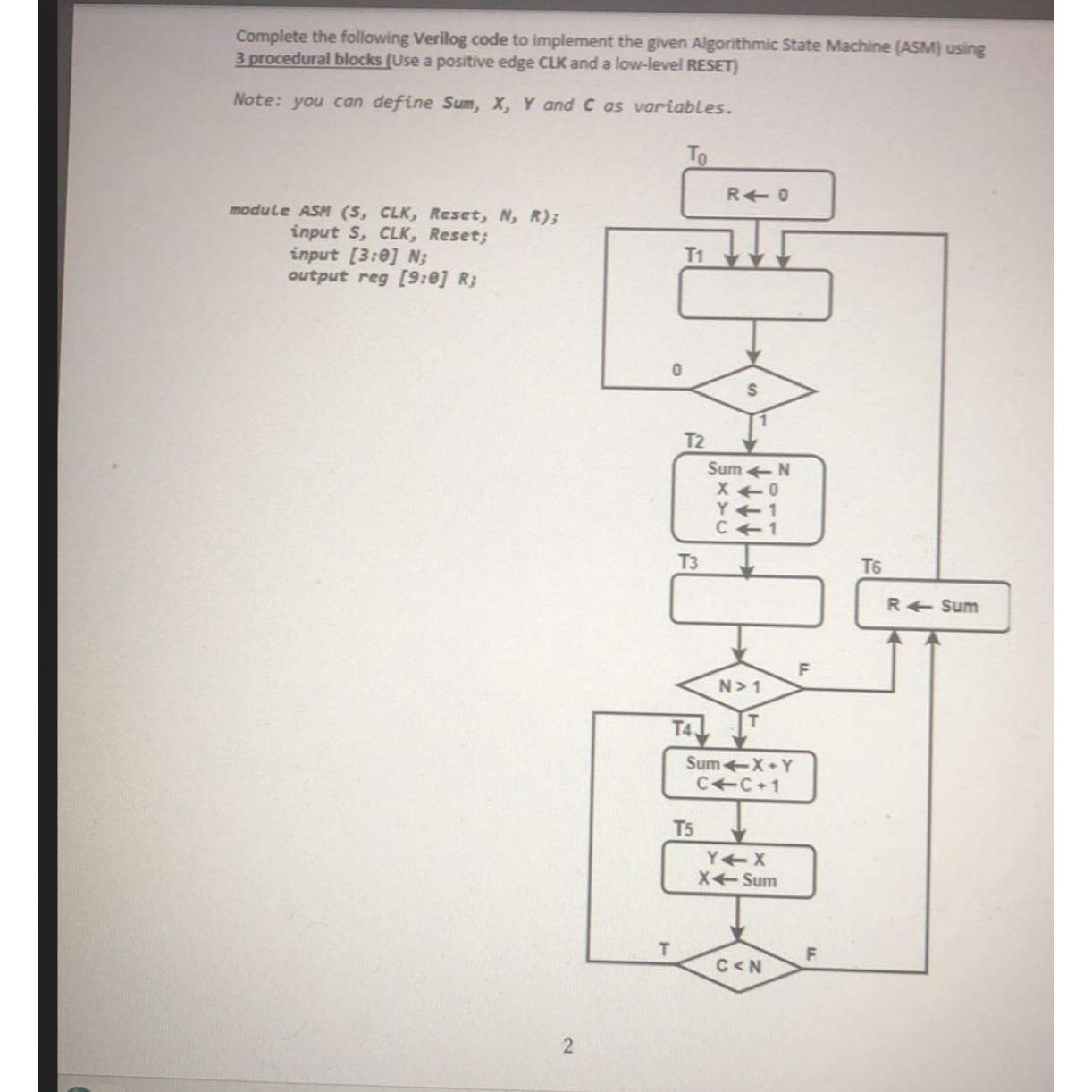

Complete the following Verilog code to implement the given Algorithmic State Machine (ASM) using 3 procedural blocks (Use a positive edge CLK and a

Complete the following Verilog code to implement the given Algorithmic State Machine (ASM) using 3 procedural blocks (Use a positive edge CLK and a low-level RESET) Note: you can define Sum, X, Y and C as variables. module ASM (S, CLK, Reset, N, R); input S, CLK, Reset; input [3:0] N; output reg [9:0] R; 2 T To R40 T1 T2 Sum N X40 Y+1 C+1 T3 T6 R < < Sum F N> 1 T T4 Sum-X+Y C+C+1 T5 Y

Step by Step Solution

3.40 Rating (156 Votes )

There are 3 Steps involved in it

Step: 1

Heres the Verilog code completing the given Algor...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Calculus

Authors: Ron Larson, Bruce H. Edwards

10th Edition

1285057090, 978-1285057095

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App