Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Consider a pipeline in a processor that has 4 stages: (1) instruction fetch and decode - 120 ns (2) calculate and fetch operand address

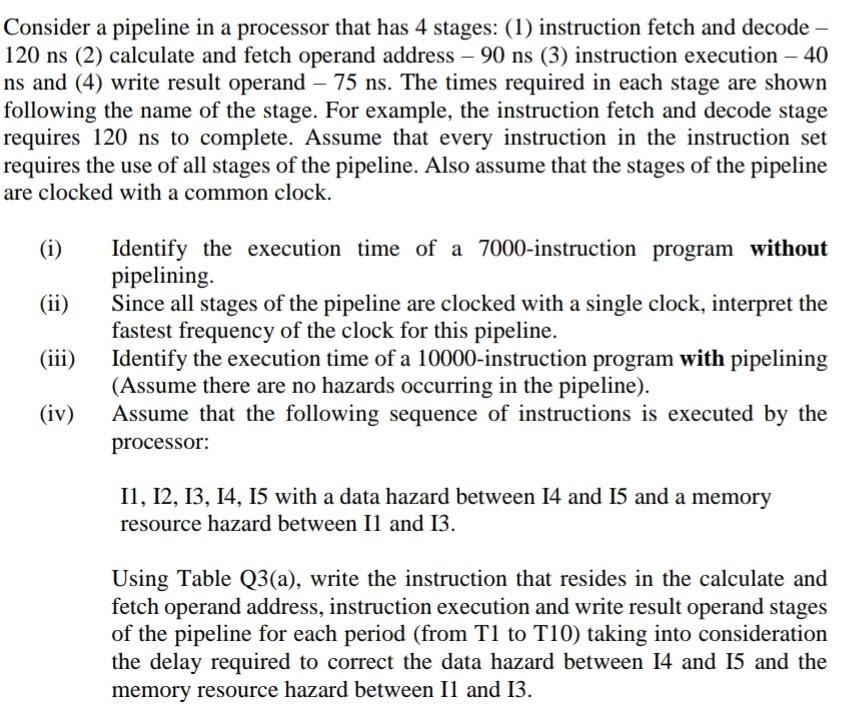

Consider a pipeline in a processor that has 4 stages: (1) instruction fetch and decode - 120 ns (2) calculate and fetch operand address - 90 ns (3) instruction execution - 40 ns and (4) write result operand - 75 ns. The times required in each stage are shown following the name of the stage. For example, the instruction fetch and decode stage requires 120 ns to complete. Assume that every instruction in the instruction set requires the use of all stages of the pipeline. Also assume that the stages of the pipeline are clocked with a common clock. (i) (ii) Identify the execution time of a 7000-instruction program without pipelining. Since all stages of the pipeline are clocked with a single clock, interpret the fastest frequency of the clock for this pipeline. (iii) Identify the execution time of a 10000-instruction program with pipelining (Assume there are no hazards occurring in the pipeline). (iv) Assume that the following sequence of instructions is executed by the processor: 11, 12, 13, 14, 15 with a data hazard between 14 and 15 and a memory resource hazard between Il and 13. Using Table Q3(a), write the instruction that resides in the calculate and fetch operand address, instruction execution and write result operand stages of the pipeline for each period (from T1 to T10) taking into consideration the delay required to correct the data hazard between 14 and 15 and the memory resource hazard between Il and 13.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started