Question

Consider the following processor where fetch unit can fetch and decode up to four instructions at each cycle depending on available slots in pre-issue buffer.

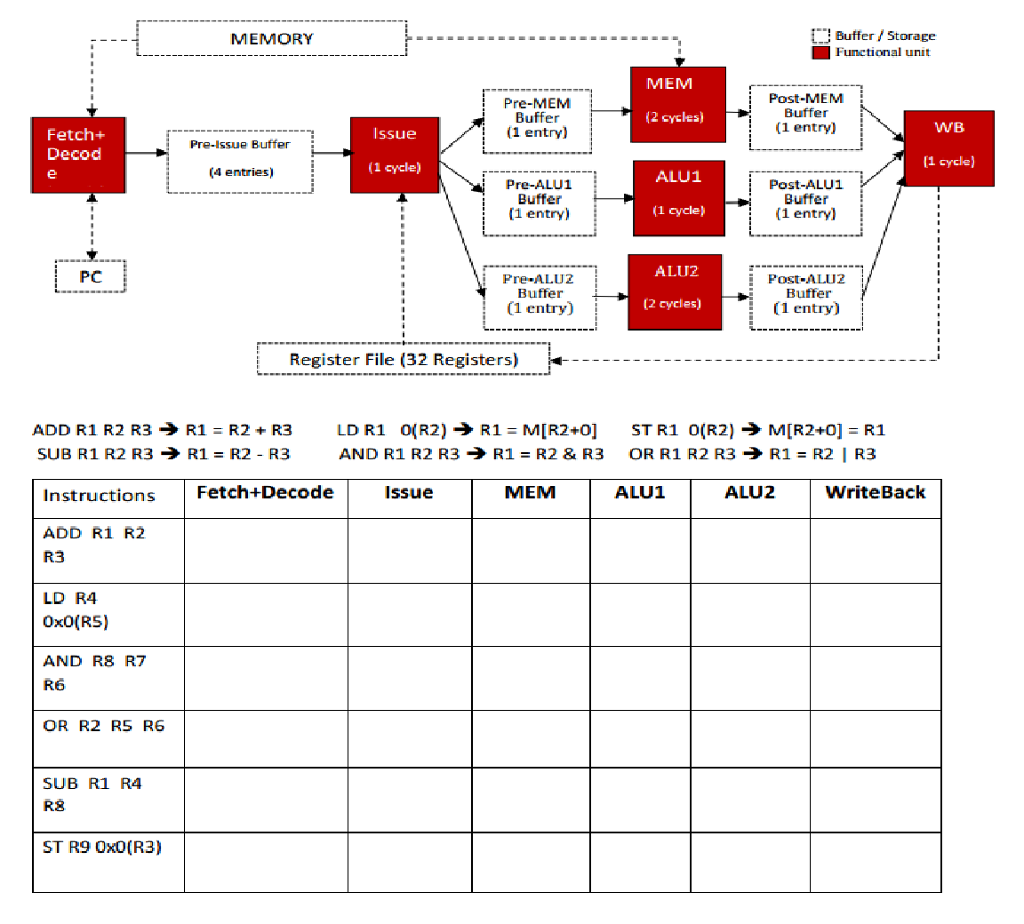

Consider the following processor where fetch unit can fetch and decode up to four instructions at each cycle depending on available slots in pre-issue buffer. The Issue unit can issue up to three instructions per cycle (one to ALU1 pipeline, one to ALU2 pipeline and another to MEM pipeline, if respective buffer is empty). Issue unit performs reading of source operands as well as all hazard (data and structural) detections before issuing the instruction(s). ALU1 supports logical operations (AND and OR) and consumes one cycle. ALU2 supports arithmetic instructions (ADD and SUB) and consumes two cycles. MEM unit supports memory instructions (LD and ST) that requires two cycles (first cycle for address calculation and second cycle for memory access). Data cannot be written and read in the same cycle. No data forwarding. The writeback (WB) unit can complete (write results, if applicable) up to three instructions (one of each type) per cycle. As you can see that both MEM and ALU2 consumes two cycles, therefore, once an instruction enters that unit, it keeps that unit busy for two consecutive cycles. When a unit is busy, it cannot accept any new instructions. When a unit starts execution, it immediately removes the instruction(s) from its input buffer, and the unit writes to the output buffer once it completes execution. For example, if Pre-MEM buffer has LD (or ST) instruction in the beginning of clock cycle 67 and MEM is free, MEM removes the instruction from Pre-MEM buffer in the beginning of clock cycle 67 and starts execution. However, MEM remains busy for clock cycle 67 and 68, and writes the result in Post-MEM buffer at the end of clock cycle 68. Note that MEM cannot start executing a new LD (or ST) instruction in the beginning of clock cycle 68, even if there is a new instruction waiting in PreMEM buffer in the beginning of clock cycle 68 (issued by the Issue unit at the end of clock cycle 67). The buffers (or memory/register file) do not consume any clock cycles, they are place holders. Only functional units (Fetch+Decode, Issue, MEM, ALU1, ALU2 and WB) consume clock cycles (as outlined above). Please pay attention to the fact that each buffer has one or four entries (as indicated in the figure), therefore, it may be necessary to stall a specific unit and its predecessors at a specific cycle to avoid data loss or to ensure functional correctness. Complete the following entries for each instruction for the architecture shown above. Each entry in the table contains the clock cycle number when that particular task was done/completed for that particular instruction as well as indicate hazard information or other reasons for stall, if any. Since each instruction is either ALU1, ALU2 or MEM type, only one of them will have value for each row. For example, if an instruction is of ALU1 type, the value in ALU1 column will indicate the cycle when that instruction is completed (ALU2 and MEM should not have any values in this example). Do not delay any computation unless it is required due to hazards or other constraints described above. In other words, push the instructions through the pipeline as fast as possible without violating any of the above-mentioned constraints.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started