Answered step by step

Verified Expert Solution

Question

1 Approved Answer

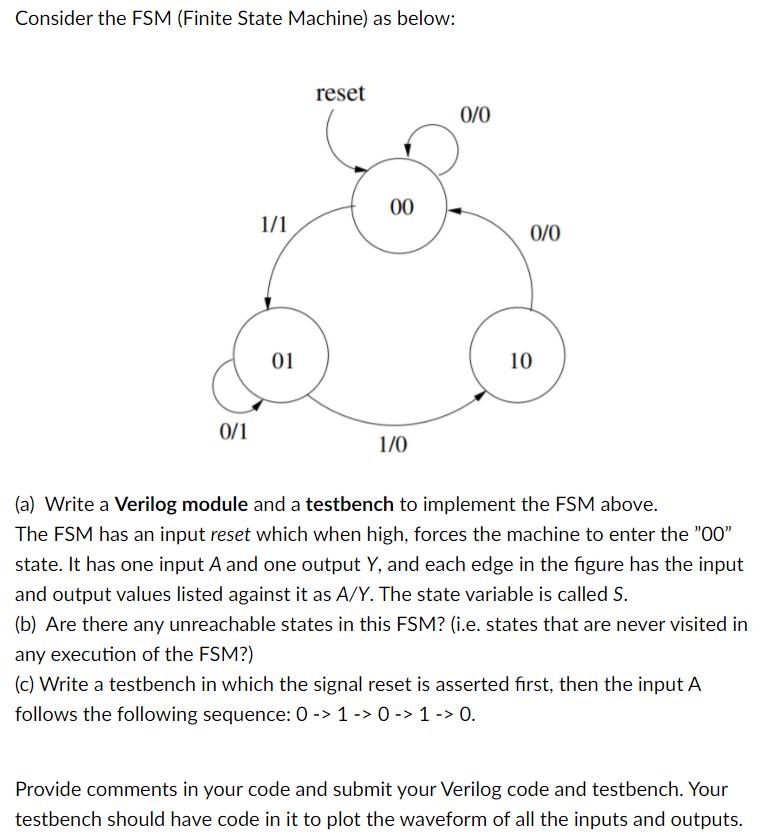

Consider the FSM (Finite State Machine) as below: 0/1 1/1 01 reset 00 1/0 0/0 0/0 10 (a) Write a Verilog module and a

Consider the FSM (Finite State Machine) as below: 0/1 1/1 01 reset 00 1/0 0/0 0/0 10 (a) Write a Verilog module and a testbench to implement the FSM above. The FSM has an input reset which when high, forces the machine to enter the "00" state. It has one input A and one output Y, and each edge in the figure has the input and output values listed against it as A/Y. The state variable is called S. (b) Are there any unreachable states in this FSM? (i.e. states that are never visited in any execution of the FSM?) (c) Write a testbench in which the signal reset is asserted first, then the input A follows the following sequence: 0 -> 1 ->0 -> 1 -> 0. Provide comments in your code and submit your Verilog code and testbench. Your testbench should have code in it to plot the waveform of all the inputs and outputs.

Step by Step Solution

★★★★★

3.43 Rating (153 Votes )

There are 3 Steps involved in it

Step: 1

edge detectorvisualTestv module edge detectorvisualtest input wire clock...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started