Answered step by step

Verified Expert Solution

Question

1 Approved Answer

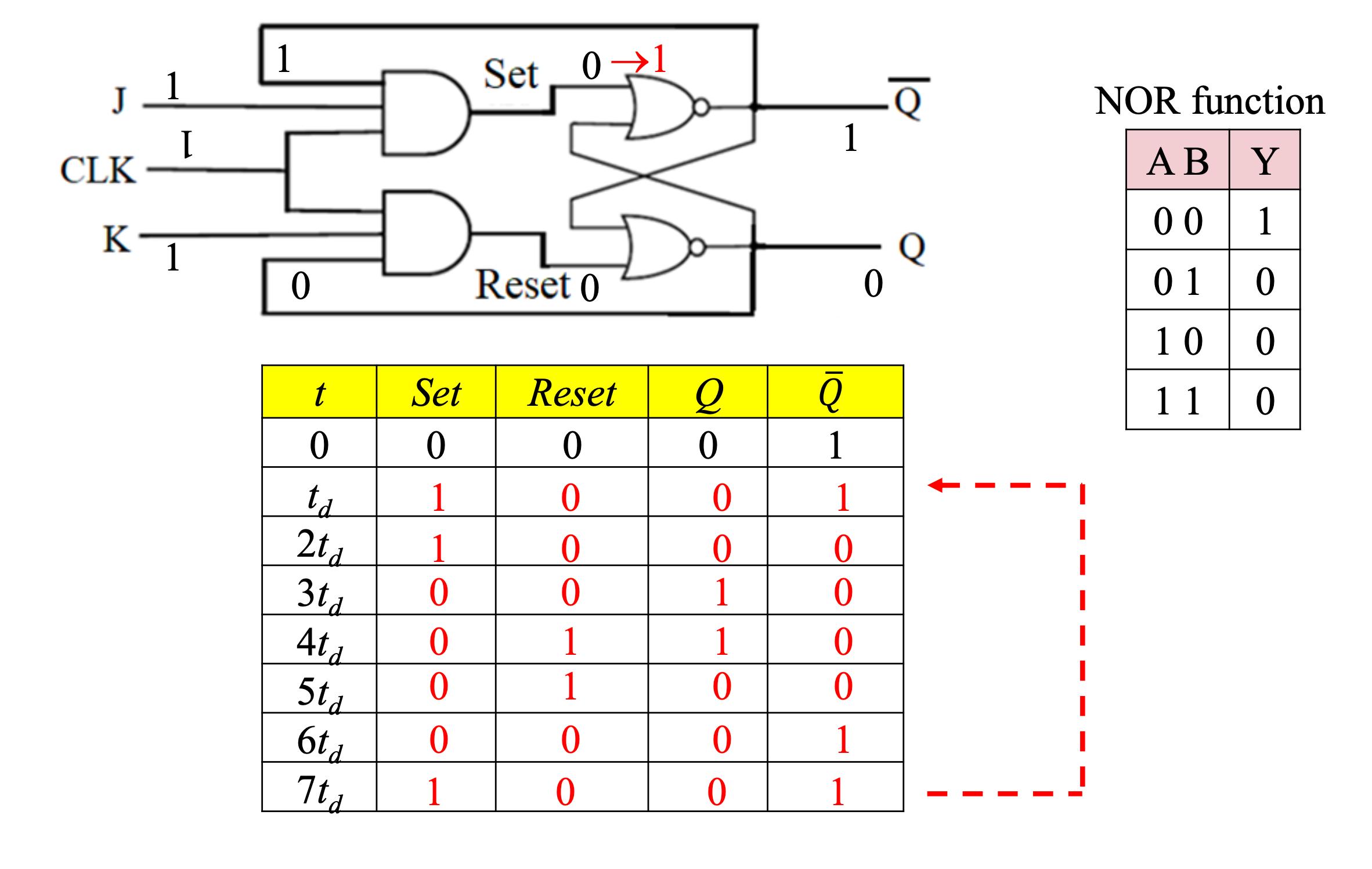

Convert it to JK flip-flop by adding the necessary decoding logic. Merge the decoding logic with the logic gates of the SR flip-flop. Initially, the

Convert it to JK flip-flop by adding the necessary

decoding logic. Merge the decoding logic with the logic gates of the SR flip-flop.

Initially, the flip-flop is at a reset state with J and K at zero. When the clock goes high,

J and K are simultaneously brought to logic “1” for a period ten times longer than the propagation delay of a logic gate. Show the effects of this on the Q and Q’ outputs with the aid of a timing diagram. Assume that all the gates in the circuit have the same propagation delay.

J CLK K 1 I 1 0 t 0 ta 2ta 3td Ata 5ta 6ta 7td 0 0 0 Set Set Reset 0 0 1 0 1 0 0 0 1 0 1 Reset 0 1 1 0 0 Q 0 0 0 1 1 0 0 0 1 Q 1 1 0 0 0 0 1 1 0 lo Q NOR function AB Y 0 0 1 01 0 10 0 11 0

Step by Step Solution

There are 3 Steps involved in it

Step: 1

SureI can help you convert the SR flipflop to a JK flipflop and show the effects on the Q and Q outp...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started