Answered step by step

Verified Expert Solution

Question

1 Approved Answer

cse 1 2 0 _ spring For the following questions, it v Mq 1 M 2 VXwmNNzQoxs 8 SjR 8 sfAR / edit Calibri 1

csespring

For the following questions, it v

MqMVXwmNNzQoxsSjRsfARedit

Calibri

B

I

U

A

harr

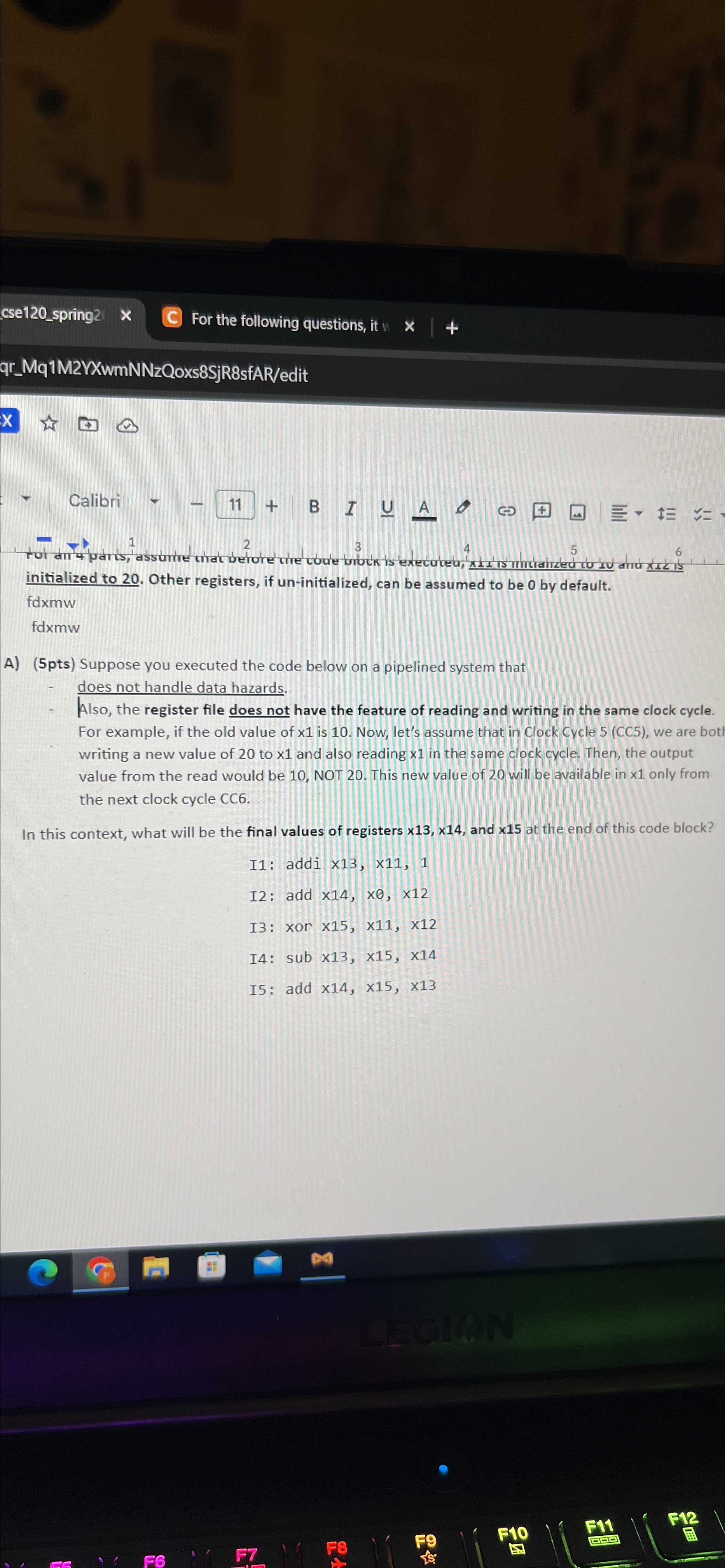

initialized to Other registers, if uninitialized, can be assumed to be by default.

fdxmw

fdxmw

Apts Suppose you executed the code below on a pipelined system that

does not handle data hazards.

Also, the register file does not have the feature of reading and writing in the same clock cycle. For example, if the old value of is Now, let's assume that in Clock Cycle CC we are bot writing a new value of to and also reading in the same clock cycle. Then, the output value from the read would be NOT This new value of will be available in only from the next clock cycle CC

In this context, what will be the final values of registers and at the end of this code block?

: addi

: add

: xor

: sub

: add

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started