Question

Design a MIPS processor supporting only the lw and the mgt rs, rt, rd instruction. The mqt rs, rt, rd instruction does the following: if

Design a MIPS processor supporting only the lw and the mgt rs, rt, rd instruction. The mqt rs, rt, rd instruction does the following:

if rs >= rt, rd is set to be rs; otherwise the next PC is set to be rt.

For example,

- if rs and rt are 20 and 8 respectively, rd will be set to 20, and PC will be PC+4.

- if rs and rt are 20 and 32 respectively, rd will not be changed, and PC will be 32.

In this problem, the simplifying assumption is that the values in rs and rt are always in [-230,230].

For this problem, assume that the opcode of lw is 000000 and the opcode of mgt is 100000.

Recall that in MIPS, ALUCtrl is 0000 for and, 0001 for or, 0100 for add, 0110 for sub.

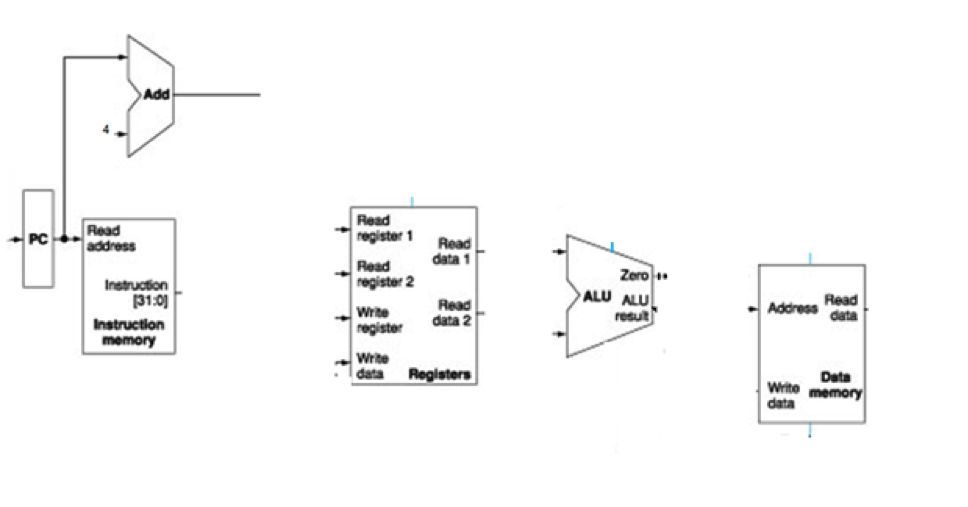

- (30 points) Show the data path of this processor, add 2-1 MUX when necessary. Besides a group of wires, please show clearly the indices of the bits.

- (20 points) The control signals include ALUCtrl, RegWrite, and the signals to control the added 2-1 MUX. Please fill in the table (you should not need more than 4 2-1 MUXes). In case of dont care, write down 0. Then write down the logic functions for RegWrite and the MUXCtrls. Certain bits in the instruction or in ALUResult can be denoted as instruct[31].

|

| lw | mgt (rs >= rt) | mgt (rs |

| ALUCtrl |

|

|

|

| RegWrite |

|

|

|

| MUXCtrl1 |

|

|

|

| MUXCtrl2 |

|

|

|

| MUXCtrl3 |

|

|

|

| MUXCtrl4 |

|

|

|

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started