Answered step by step

Verified Expert Solution

Question

1 Approved Answer

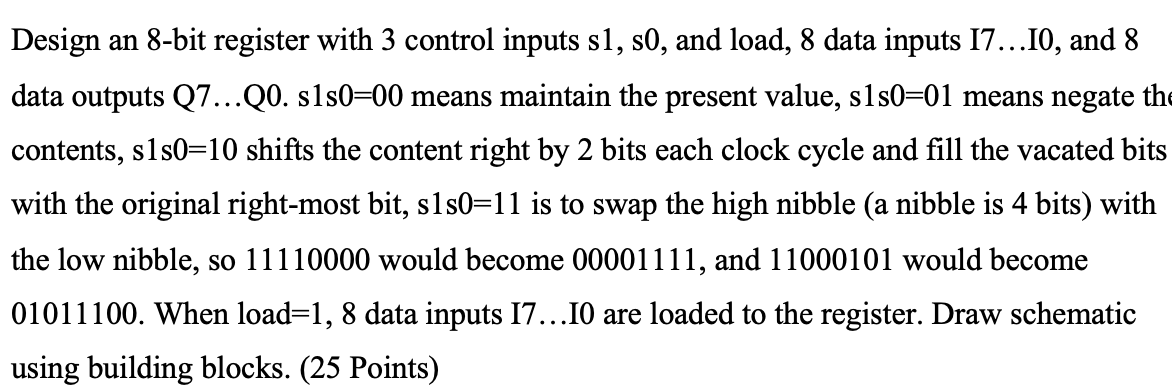

Design an 8 - bit register with 3 control inputs s 1 , s 0 , and load, 8 data inputs I 7 . .

Design an bit register with control inputs and load, data inputs II and

data outputs dotsQ ss means maintain the present value, means negate th

contents, shifts the content right by bits each clock cycle and fill the vacated bits

with the original rightmost bit, is to swap the high nibble a nibble is bits with

the low nibble, so would become and would become

When load data inputs II are loaded to the register. Draw schematic

using building blocks. Points

note that an additional signal load is added. When load data inputs II are loaded to the register.

Attention that any bus with customized order is not allowed. You can only use bus to merge your signals. Additionally, you should label the highest digit of you merged signal when using the bus to eliminate the ambiguity.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started