Question

design.sv module dff (clk, reset, d, q, qb); //write required parts here reg q; //write required parts here always @(posedge clk or posedge reset) begin

design.sv

module dff (clk, reset, d, q, qb); //write required parts here

reg q;

//write required parts here

always @(posedge clk or posedge reset) begin if (reset) begin q

testbench.sv

module test;

//write required parts here dff DFF(.clk(clk), .reset(reset), .d(d), .q(q), .qb(qb)); initial begin $dumpfile("dump.vcd"); $dumpvars(1); $display("Reset flop."); clk = 0; reset = 1; d = 1'bx; display; $display("Release reset."); d = 1; reset = 0; display;

$display("Toggle clk."); clk = 1; display; end task display; #1 $display("d:%0h, q:%0h, qb:%0h", d, q, qb); endtask

endmodule

. pls ans if u know the correct one ,othewise i will report it .thanks

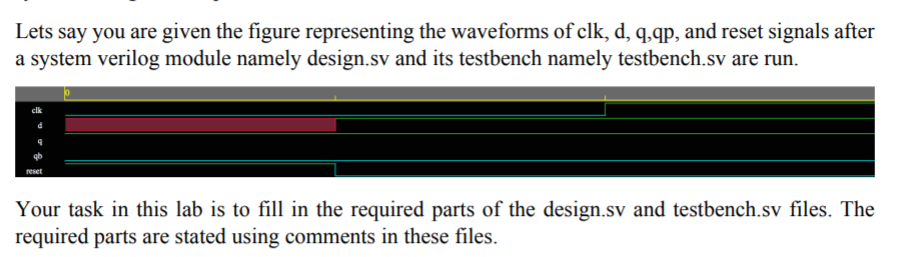

Lets say you are given the figure representing the waveforms of clk, d, q,qp, and reset signals after a system verilog module namely design.sv and its testbench namely testbench.sv are run. reset Your task in this lab is to fill in the required parts of the design.sv and testbench.sv files. The required parts are stated using comments in these filesStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started