Question

DIGITAL ELECTRONICS (verilog code) can you explain about this code and output step by step becoz i need to understand it. ------------------verilog code---------------------------- module state_machine(CLK,RESET,X,present_state,next_state,Z);

DIGITAL ELECTRONICS (verilog code) can you explain about this code and output step by step becoz i need to understand it. ------------------verilog code----------------------------

module state_machine(CLK,RESET,X,present_state,next_state,Z); input CLK,RESET,X; output [1:0]present_state,next_state; output Z; reg [1:0]present_state=2'b00,next_state=2'b00; reg Z=0; parameter A=2'b00,B=2'b01,C=2'b10,D=2'b11; always@(posedge CLK or posedge RESET) begin if (RESET) present_state

-----------------------------------test bench ----------------------------------------

module demo_ve_tb; reg CLK,RESET,X; wire [1:0]present_state; wire [1:0]next_state; wire Z; state_machine uut(.CLK(CLK),.RESET(RESET),.X(X), .present_state(present_state),.next_state(next_state),.Z(Z));

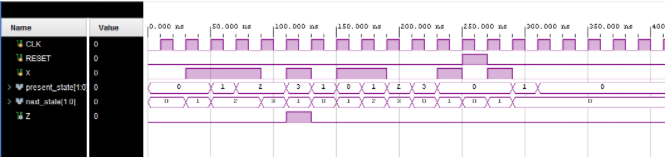

initial begin CLK=0; forever #10 CLK = ~CLK; end initial begin RESET=1'b0; X=1'b0; #30; X=1'b1; #20; X=1'b1; #20; X=1'b1; #20; X=1'b0; #20; X=1'b1; #20; X=1'b0; #20; X=1'b1; #20; X=1'b1; #20; X=1'b0; #20; X=1'b0; #20; X=1'b1; #20; X=1'b0;RESET=1'b1; #20; RESET=1'b0; X=1'b1; #20; X=1'b0; #20; X=1'b0; #20; end endmodule output waveform

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started