Answered step by step

Verified Expert Solution

Question

1 Approved Answer

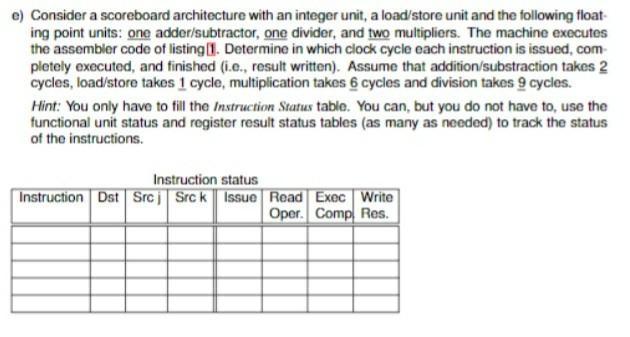

e) Consider a scoreboard architecture with an integer unit, a load/store unit and the following float- ing point units: one adder/subtractor, one divider, and

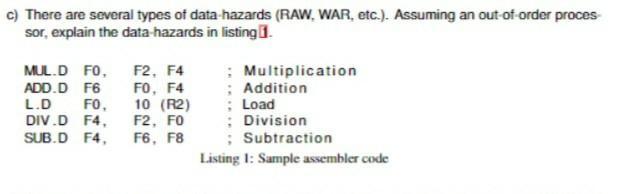

e) Consider a scoreboard architecture with an integer unit, a load/store unit and the following float- ing point units: one adder/subtractor, one divider, and two multipliers. The machine executes the assembler code of listing 1. Determine in which clock cycle each instruction is issued, com pletely executed, and finished (i.e., result written). Assume that addition/substraction takes 2 cycles, load/store takes 1 cycle, multiplication takes 6 cycles and division takes 9 cycles. Hint: You only have to fill the Instruction Status table. You can, but you do not have to, use the functional unit status and register result status tables (as many as needed) to track the status of the instructions. Instruction status Instruction Dst Srcj Srck Issue Read Exec Write Oper. Comp Res. c) There are several types of data-hazards (RAW, WAR, etc.). Assuming an out-of-order proces sor, explain the data hazards in listing. MUL.D FO, F2, F4 ADD.D F6 L.D FO, F4 FO, 10 (R2) DIV.D F4, F2, FO SUB.D F4, F6, F8 ; Multiplication ; Addition ; Load ; Division ; Subtraction Listing 1: Sample assembler code e) Consider a scoreboard architecture with an integer unit, a load/store unit and the following float- ing point units: one adder/subtractor, one divider, and two multipliers. The machine executes the assembler code of listing 1. Determine in which clock cycle each instruction is issued, com pletely executed, and finished (i.e., result written). Assume that addition/substraction takes 2 cycles, load/store takes 1 cycle, multiplication takes 6 cycles and division takes 9 cycles. Hint: You only have to fill the Instruction Status table. You can, but you do not have to, use the functional unit status and register result status tables (as many as needed) to track the status of the instructions. Instruction status Instruction Dst Srcj Srck Issue Read Exec Write Oper. Comp Res. c) There are several types of data-hazards (RAW, WAR, etc.). Assuming an out-of-order proces sor, explain the data hazards in listing. MUL.D FO, F2, F4 ADD.D F6 L.D FO, F4 FO, 10 (R2) DIV.D F4, F2, FO SUB.D F4, F6, F8 ; Multiplication ; Addition ; Load ; Division ; Subtraction Listing 1: Sample assembler code e) Consider a scoreboard architecture with an integer unit, a load/store unit and the following float- ing point units: one adder/subtractor, one divider, and two multipliers. The machine executes the assembler code of listing 1. Determine in which clock cycle each instruction is issued, com pletely executed, and finished (i.e., result written). Assume that addition/substraction takes 2 cycles, load/store takes 1 cycle, multiplication takes 6 cycles and division takes 9 cycles. Hint: You only have to fill the Instruction Status table. You can, but you do not have to, use the functional unit status and register result status tables (as many as needed) to track the status of the instructions. Instruction status Instruction Dst Srcj Srck Issue Read Exec Write Oper. Comp Res. c) There are several types of data-hazards (RAW, WAR, etc.). Assuming an out-of-order proces sor, explain the data hazards in listing. MUL.D FO, F2, F4 ADD.D F6 L.D FO, F4 FO, 10 (R2) DIV.D F4, F2, FO SUB.D F4, F6, F8 ; Multiplication ; Addition ; Load ; Division ; Subtraction Listing 1: Sample assembler code

Step by Step Solution

★★★★★

3.41 Rating (164 Votes )

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started