Answered step by step

Verified Expert Solution

Question

1 Approved Answer

EECE 144 Lab #6: 4-bit Adder/Subtractor in Verilog Introduction: A full adder circuit may be converted to an adder/subtractor with the addition of a

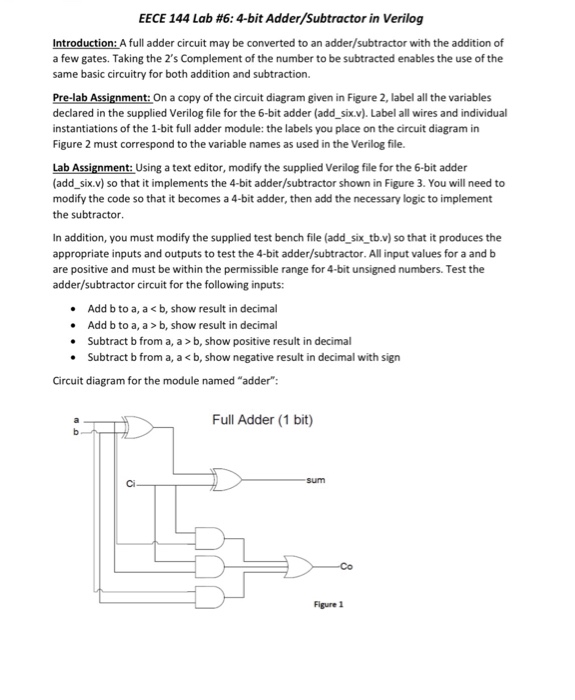

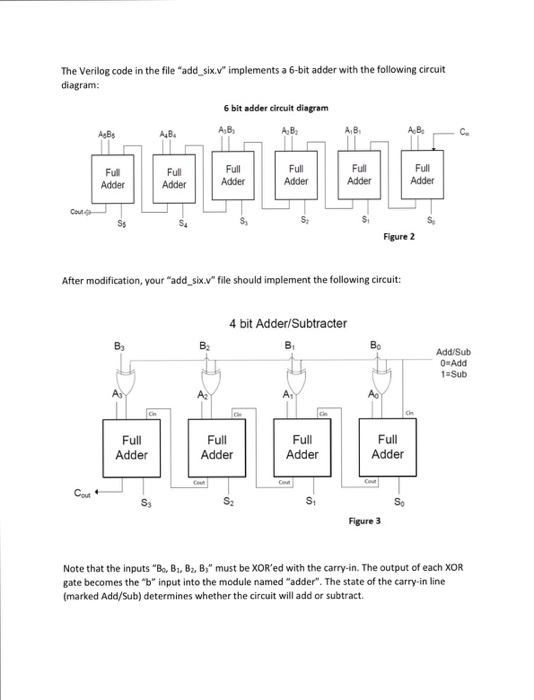

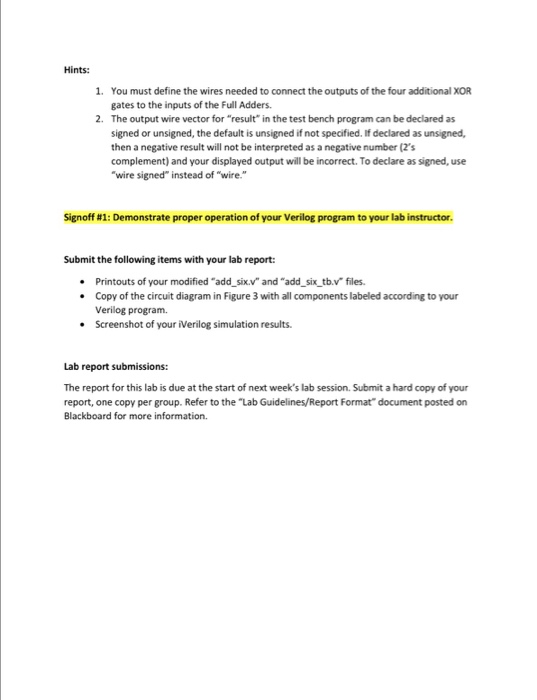

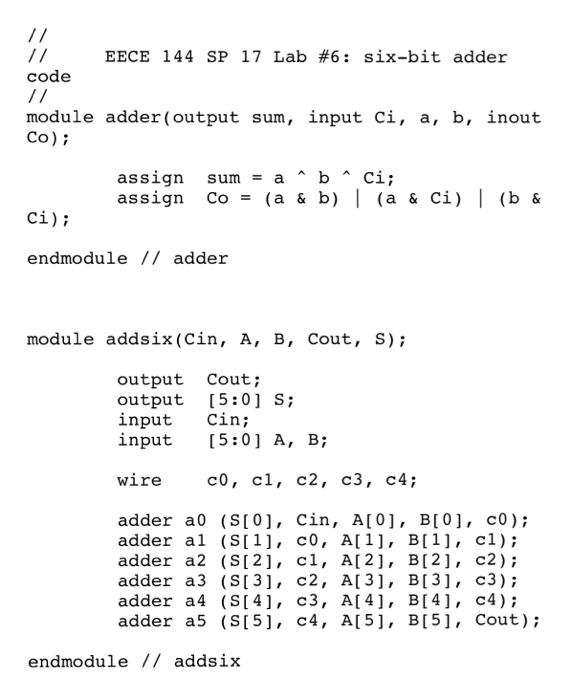

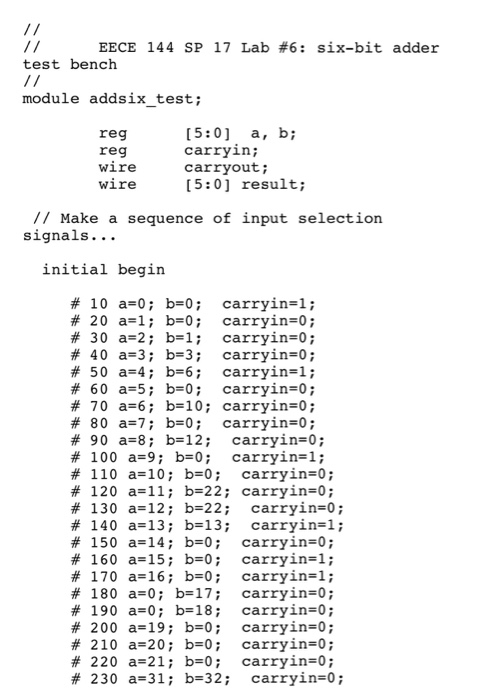

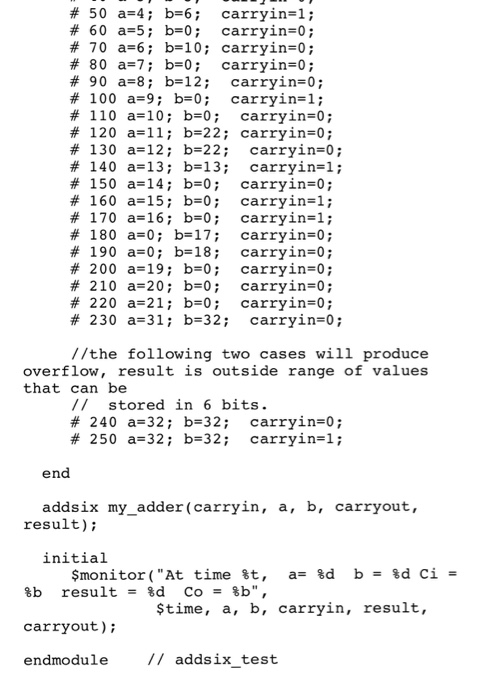

EECE 144 Lab #6: 4-bit Adder/Subtractor in Verilog Introduction: A full adder circuit may be converted to an adder/subtractor with the addition of a few gates. Taking the 2's Complement of the number to be subtracted enables the use of the same basic circuitry for both addition and subtraction. Pre-lab Assignment: On a copy of the circuit diagram given in Figure 2, label all the variables declared in the supplied Verilog file for the 6-bit adder (add_six.v). Label all wires and individual instantiations of the 1-bit full adder module: the labels you place on the circuit diagram in Figure 2 must correspond to the variable names as used in the Verilog file. Lab Assignment: Using a text editor, modify the supplied Verilog file for the 6-bit adder (add_six.v) so that it implements the 4-bit adder/subtractor shown in Figure 3. You will need to modify the code so that it becomes a 4-bit adder, then add the necessary logic to implement the subtractor. In addition, you must modify the supplied test bench file (add_six_tb.v) so that it produces the appropriate inputs and outputs to test the 4-bit adder/subtractor. All input values for a and b are positive and must be within the permissible range for 4-bit unsigned numbers. Test the adder/subtractor circuit for the following inputs: Add b to a, a b, show result in decimal Subtract b from a, a>b, show positive result in decimal Subtract b from a, a The Verilog code in the file "add_six.v" implements a 6-bit adder with the following circuit diagram: Cout AB Cout Full Adder So B A4B Full Adder Full Adder S4 6 bit adder circuit diagram AB B Full Adder $ Full Adder AB After modification, your "add_six.v" file should implement the following circuit: S Full Adder 4 bit Adder/Subtracter B Full Adder AB Cout Full Adder S $ Bo Full Adder Cout Figure 3 Figure 2 AB So Full Adder Add/Sub 0 Add 1=Sub Note that the inputs "B, B, B2, B3" must be XOR'ed with the carry-in. The output of each XOR gate becomes the "b" input into the module named "adder". The state of the carry-in line (marked Add/Sub) determines whether the circuit will add or subtract. Hints: 1. You must define the wires needed to connect the outputs of the four additional XOR gates to the inputs of the Full Adders. 2. The output wire vector for "result" in the test bench program can be declared as signed or unsigned, the default is unsigned if not specified. If declared as unsigned, then a negative result will not be interpreted as a negative number (2's complement) and your displayed output will be incorrect. To declare as signed, use "wire signed" instead of "wire." Signoff #1: Demonstrate proper operation of your Verilog program to your lab instructor. Submit the following items with your lab report: Printouts of your modified "add_six.v" and "add_six_tb.v" files. Copy of the circuit diagram in Figure 3 with all components labeled according to your Verilog program. Screenshot of your iVerilog simulation results. Lab report submissions: The report for this lab is due at the start of next week's lab session. Submit a hard copy of your report, one copy per group. Refer to the "Lab Guidelines/Report Format" document posted on Blackboard for more information. // // code EECE 144 SP 17 Lab #6: six-bit adder module adder(output sum, input Ci, a, b, inout Co); Ci); assign sum = a^ b^ Ci; assign Co= (a & b) | (a & Ci) | (b & endmodule // adder module addsix (Cin, A, B, Cout, S); output Cout; output input Cin; input wire [5:0] S; [5:0] A, B; c0, c1, c2, c3, c4; adder a0 (S[0], Cin, A[0], B[0], 0); adder al (S[1], c0, A[1], B[1], cl); adder a2 (S[2], cl, A[2], B[2], C2); adder a3 (S[3], c2, A[3], B[3], c3); adder a4 (S[4], c3, A[4], B[4], adder a5 (S[5], c4, A[5], B[5], endmodule // addsix 4); Cout); // EECE 144 SP 17 Lab # 6: six-bit adder test bench // module addsix_test; reg reg wire wire [5:0] a, b; carryin; carryout; [5:0] result; // Make a sequence of input selection signals... initial begin # 10 a=0; b=0; carryin=1; # 20 a=1; b=0; #30 a 2; b=1; # 40 a=3; b=3; # 50 a=4; b=6; # 60 a=5; b=0; # 70 a=6; b=10; # 80 a=7; b=0; # 90 a=8; b= 12; #100 a 9; b=0; # 110 a 10; b=0; # 120 a=11; b=22; # 130 a 12; b=22; # 140 a13; b=13; # 150 a 14; b=0; # 160 a 15; b=0; # 170 a 16; b=0; # 180 a=0; b=17; # 190 a=0; b=18; # 200 a 19; b=0; # 210 a=20; b=0; # 220 a 21; b=0; # 230 a=31; b=32; carryin=0; carryin=0; carryin=0; carryin=1; carryin=0; carryin=0; carryin=0; carryin=0; carryin=1; carryin=0; carryin=0; carryin=0; carryin=1; carryin=0; carryin=1; carryin=1; carryin=0; carryin=0; carryin=0; carryin=0; carryin=0; carryin=0; # 50 a=4; b=6; carryin=1; # 60 a=5; b=0; carryin=0; # 70 a=6; b=10; carryin=0; # 80 a=7; b=0; carryin=0; #90 a 8; b=12; carryin=0; # 100 a 9; b=0; carryin=1; # 110 a 10; b=0; carryin=0; # 120 a 11; b=22; carryin=0; # 130 a 12; b=22; carryin=0; # 140 a 13; b=13; carryin=1; #150 a 14; b=0; carryin=0; # 160 a 15; b=0; carryin=1; # 170 a 16; b=0; carryin=1; # 180 a=0; b=17; carryin=0; #190 a=0; b=18; carryin=0; #200 a 19; b=0; carryin=0; # 210 a 20; b=0; carryin=0; # 220 a 21; b=0; carryin=0; # 230 a 31; b=32; carryin=0; //the following two cases will produce overflow, result is outside range of values that can be // stored in 6 bits. #240 a=32; b=32; carryin=0; # 250 a=32; b=32; carryin=1; end addsix my_adder (carryin, a, b, carryout, result); initial $monitor ("At time t, a=%d b = %d Ci = Co= %b", $time, a, b, carryin, result, %b result = %d carryout); endmodule // addsix_test

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started