Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Fig 4.18 provided in here 3. [20] In our example Y86-64 programs, such as the Sum function shown in Figure 4.6, we encounter many cases

Fig 4.18 provided in here

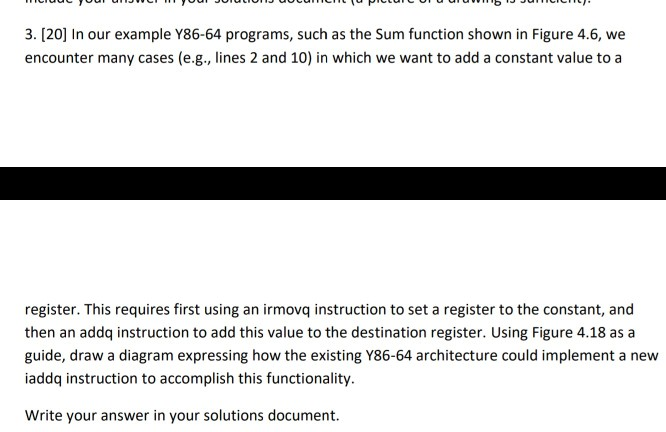

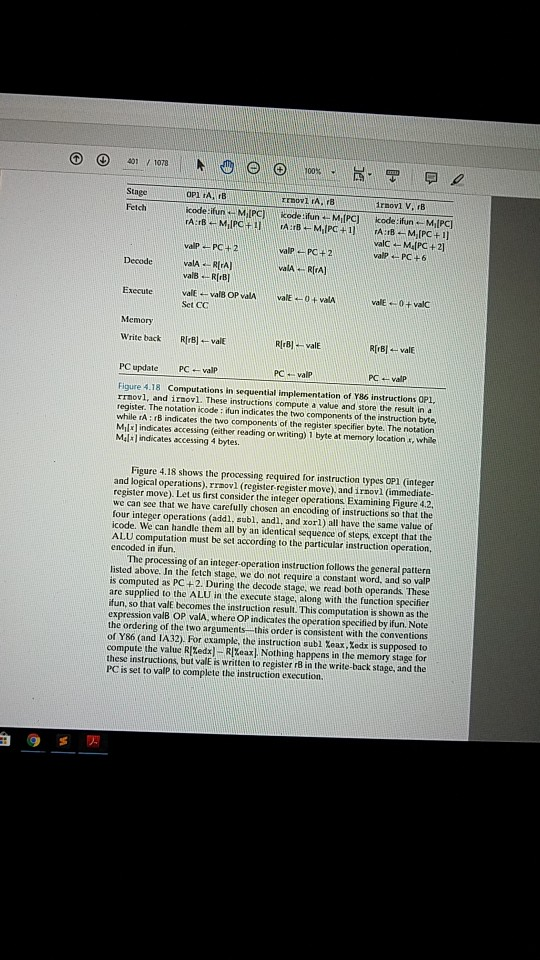

3. [20] In our example Y86-64 programs, such as the Sum function shown in Figure 4.6, we encounter many cases (e.g., lines 2 and 10) in which we want to add a constant value to a register. This requires first using an irmovq instruction to set a register to the constant, and then an addq instruction to add this value to the destination register. Using Figure 4.18 as a guide, draw a diagram expressing how the existing Y86-64 architecture could implement a new iaddq instruction to accomplish this functionality Write your answer in your solutions document 401 V 1078 Stnge OP1 TA rrnovi rA.FB Fetch code:ifun MPC) ode:funMIPC) code:ifun MIPCI valp PC + 2 valP PC +2 Decode valA RhAI valARA] valEvalB OP valvale0 +vala Set CC vale O+ valc Memory Write backRrBl-val PC update PCvalp PC valP Figure 4.18 Computations in sequential implementation of Y86 instructions OPI rrnovl, and irnovl. These instructions compute a value and store the result in a register. The notation icode : ifun indicates the two components of the instruction byte while rA :rB indicates the two components of the register specifier byte. The notation Mr] indicates accessing (either reading or writing) 1 byte at memory location, while M4l l indicates accessing 4 bytes. Figure 4.18 shows the processing required for instruction types OPl (integer and logical operations), rrmovl (register-register move), and irnovl (immediate- register move). Let us first consider the integer operations Examining Figure 4.2 we can see that we have carefully chosen an encoding of instructions so that the four integer operations (addl, subl, andl, and xorl) all have the same value of icode. We can handle them all by an identical sequence of steps except that the ALU computation must be set according to the particular instruction operation encoded in ifun. The processing of an integer-operation instruction follows the general pattern listed above. In the fetch stage, we do not require a constant word, and so val is computed as PC +2. During the decode stage, we read both operands These are supplied to the ALU in the execute stage, along with the function specifier ifun, so that valE becomes the instruction result. This computation is shown as the expression valB OP valA. where OP indicates the operation specified by ifun. Note the ordering of the two arguments this order is consistent with the conventions of Y86 (and IA32) For example, the instruction subl eax,Xedx is supposed to compute the value Rl edx) R[Keaz). Nothing happens in the memory stage for these instructions, but valE is written to register rB in the write-back stage, and the PC is set to valP to complete the instruction execution 3. [20] In our example Y86-64 programs, such as the Sum function shown in Figure 4.6, we encounter many cases (e.g., lines 2 and 10) in which we want to add a constant value to a register. This requires first using an irmovq instruction to set a register to the constant, and then an addq instruction to add this value to the destination register. Using Figure 4.18 as a guide, draw a diagram expressing how the existing Y86-64 architecture could implement a new iaddq instruction to accomplish this functionality Write your answer in your solutions document 401 V 1078 Stnge OP1 TA rrnovi rA.FB Fetch code:ifun MPC) ode:funMIPC) code:ifun MIPCI valp PC + 2 valP PC +2 Decode valA RhAI valARA] valEvalB OP valvale0 +vala Set CC vale O+ valc Memory Write backRrBl-val PC update PCvalp PC valP Figure 4.18 Computations in sequential implementation of Y86 instructions OPI rrnovl, and irnovl. These instructions compute a value and store the result in a register. The notation icode : ifun indicates the two components of the instruction byte while rA :rB indicates the two components of the register specifier byte. The notation Mr] indicates accessing (either reading or writing) 1 byte at memory location, while M4l l indicates accessing 4 bytes. Figure 4.18 shows the processing required for instruction types OPl (integer and logical operations), rrmovl (register-register move), and irnovl (immediate- register move). Let us first consider the integer operations Examining Figure 4.2 we can see that we have carefully chosen an encoding of instructions so that the four integer operations (addl, subl, andl, and xorl) all have the same value of icode. We can handle them all by an identical sequence of steps except that the ALU computation must be set according to the particular instruction operation encoded in ifun. The processing of an integer-operation instruction follows the general pattern listed above. In the fetch stage, we do not require a constant word, and so val is computed as PC +2. During the decode stage, we read both operands These are supplied to the ALU in the execute stage, along with the function specifier ifun, so that valE becomes the instruction result. This computation is shown as the expression valB OP valA. where OP indicates the operation specified by ifun. Note the ordering of the two arguments this order is consistent with the conventions of Y86 (and IA32) For example, the instruction subl eax,Xedx is supposed to compute the value Rl edx) R[Keaz). Nothing happens in the memory stage for these instructions, but valE is written to register rB in the write-back stage, and the PC is set to valP to complete the instruction executionStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started