Answered step by step

Verified Expert Solution

Question

1 Approved Answer

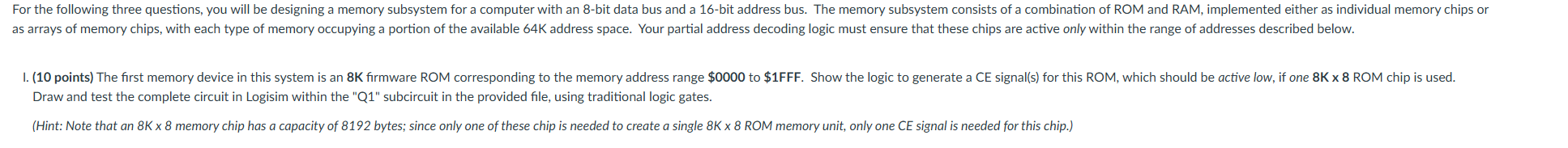

For the following three questions, you will be designing a memory subsystem for a computer with an 8 - bit data bus and a 1

For the following three questions, you will be designing a memory subsystem for a computer with an bit data bus and a bit address bus. The memory subsystem consists of a combination of ROM and RAM, implemented either as individual memory chips or as arrays of memory chips, with each type of memory occupying a portion of the available K address space. Your partial address decoding logic must ensure that these chips are active only within the range of addresses described below.

points The first memory device in this system is an K firmware ROM corresponding to the memory address range $ to $FFF Show the logic to generate a CE signals for this ROM, which should be active low, if one K x ROM chip is used.Draw and test the complete circuit in Logisim within the Q subcircuit in the provided file, using traditional logic gates.

Hint: Note that an memory chip has a capacity of bytes; since only one of these chip is needed to create a single ROM memory unit, only one CE signal is needed for this chip.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started