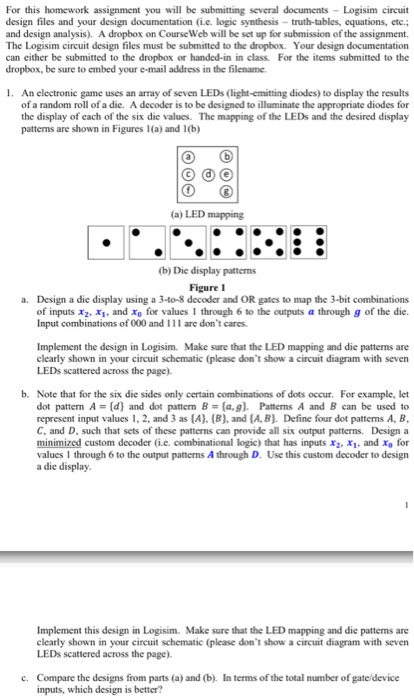

For this homework assignment, you will be submitting several documents - Logistic circuit design files and your design documentation (i.e. lope synthesis truth-tables, equations, etc.; and design analysis), A drop box on Course Web will be set up for submission of the assignment. The Logistic circuit design files must be submitted to the drop box Your design documentation can either be submitted to the drop box or handed-in in class. For the items submitted to the drop box. be sure to embed your e-mail address in the filename an electronic game uses an array of seven LEDs (light-emitting diodes) to display the results of a random roll of a die. A decoder is to be designed to illuminate the appropriate diodes for the display of each of the six die values. the mapping of the LEDs and the desired display patterns arc shown in Figures 1(a) and 1(b) Design a die display using a 3-to-X decoder and OR gates to map the 3-bit combinations of inputs x_2. x_1 and x_0 for values 1 through 6 to the outputs a through g of the die. Input combinations of 000 and 111 arc don't cares. Implement the design in Logistic. Make sure that the LED mapping and die patterns arc clearly shown in your circuit schematic (please don't show a circuit diagram with seven LEDs scattered across the page). Note that for the six die sides only certain combinations of dots occur. For example, let dot pattern A = (d) and dot pattern B = (a. g} Patterns A and B can be used to represent input values 1. 2. and 3 as (A). (8). and {A. B}. Define four dot patterns A. B. C. and D. such that sets of these patterns can provide all six output patterns. Design a minimized custom decoder (i.e. combinational lope) that has inputs x_2. x_1. and x_0 for values 1 through 6 to the output patterns A through D Use this custom decoder to design a die display. Implement this design in Logistic. Make sure that the LEO mapping and die patterns arc clearly shown in your circuit schematic (please don't show a circuit diagram with seven LEDs scattered across the page). Compare the designs from parts (a) and (b). inputs, which design is better? in terms of the total number of gate dev ice