Question: G (23 points) e Search Tex | Welcome t G (23 points) | 90005a.pdf e Chegg Stur 2A Brief Introd X (2) Faceboc -) file:///C/Users/Alex/Downloads/PTQ%20(1).pdf

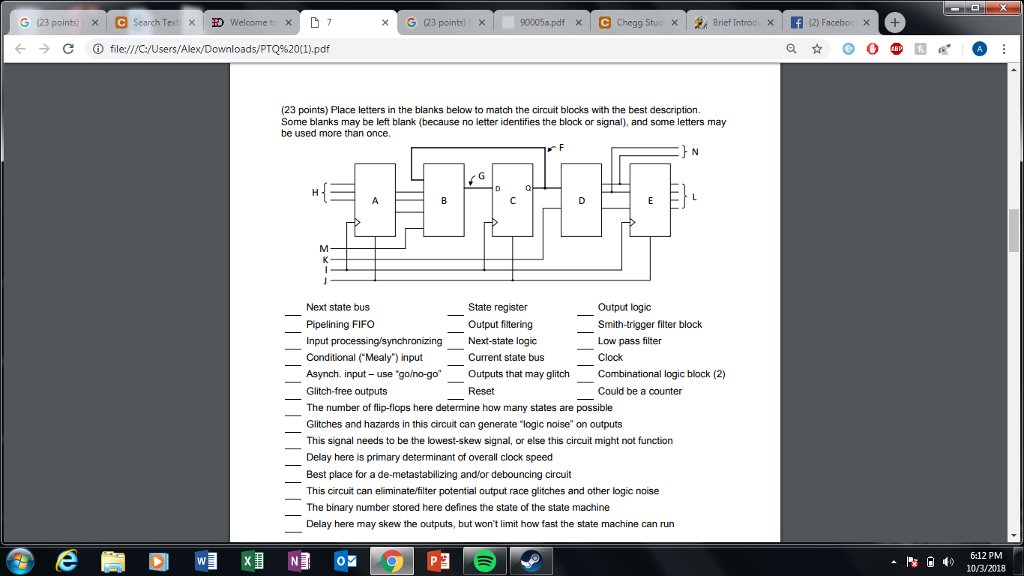

G (23 points) e Search Tex | Welcome t G (23 points) | 90005a.pdf e Chegg Stur 2A Brief Introd X (2) Faceboc -) file:///C/Users/Alex/Downloads/PTQ%20(1).pdf (23 points) Place letters in the blanks below to match the circuit blocks with the best description. Some blanks may belk (because no letter identifies the block or signal), and some letters may be used more than once Next state bus State register Output filtering Next-state logic Output logic Smith-trigger filter block Low pass filter Clock Pipelining FIFO Conditional ('Mealy) input Asynch. input- use "gono-go Outputs that may glitch Combinational logic block (2) Glitch-free outputs Reset nmber of flip-flops here determine how many states are possible Glitches and hazards in this circuit can generate "logic noise" on outputs This signal needs to be the lowest-skew signal, or else this circuit might not function Delay here is primary determinant of overall clock speed Best place for a de-metastabilizing and/or debouncing circuit This circuit can eliminate/filter potential output race glitches and other logic noise he binary number stored here defines the state of the state machine Delay here may skew the outputs, but won't limit how fast the state machine can run 6:12 PM 10/3/2018 G (23 points) e Search Tex | Welcome t G (23 points) | 90005a.pdf e Chegg Stur 2A Brief Introd X (2) Faceboc -) file:///C/Users/Alex/Downloads/PTQ%20(1).pdf (23 points) Place letters in the blanks below to match the circuit blocks with the best description. Some blanks may belk (because no letter identifies the block or signal), and some letters may be used more than once Next state bus State register Output filtering Next-state logic Output logic Smith-trigger filter block Low pass filter Clock Pipelining FIFO Conditional ('Mealy) input Asynch. input- use "gono-go Outputs that may glitch Combinational logic block (2) Glitch-free outputs Reset nmber of flip-flops here determine how many states are possible Glitches and hazards in this circuit can generate "logic noise" on outputs This signal needs to be the lowest-skew signal, or else this circuit might not function Delay here is primary determinant of overall clock speed Best place for a de-metastabilizing and/or debouncing circuit This circuit can eliminate/filter potential output race glitches and other logic noise he binary number stored here defines the state of the state machine Delay here may skew the outputs, but won't limit how fast the state machine can run 6:12 PM 10/3/2018

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts