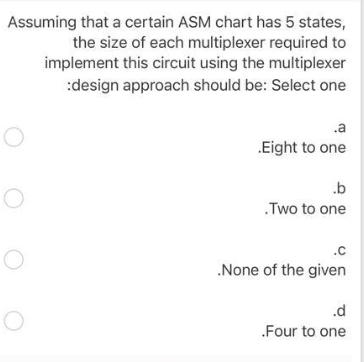

Assuming that a certain ASM chart has 5 states, the size of each multiplexer required to implement this circuit using the multiplexer :design approach

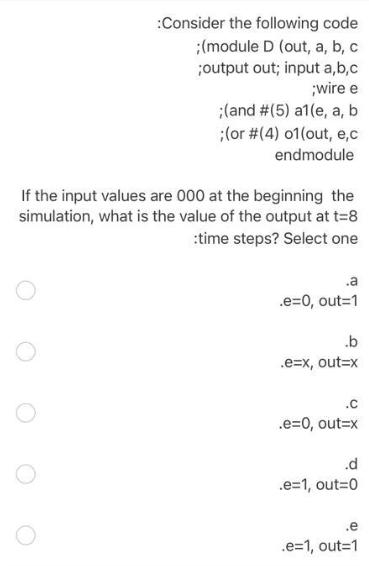

Assuming that a certain ASM chart has 5 states, the size of each multiplexer required to implement this circuit using the multiplexer :design approach should be: Select one .a Eight to one .b .Two to one .C .None of the given .d Four to one The following Verilog code defines one matrix [reg [4:0] vectr[0:15 :Select one True False :Consider the following code ;(module D (out, a, b, c ;output out; input a,b,c ;wire e ;(and #(5) a1(e, a, b ;(or #(4) o1(out, e,c endmodule If the input values are 000 at the beginning the simulation, what is the value of the output at t=8 :time steps? Select one .e=0, out=1 .b .e=x, out=x .C .e=0, out=x .d .e=1, out=0 .e=1, out=1

Step by Step Solution

3.52 Rating (155 Votes )

There are 3 Steps involved in it

Step: 1

1 The ASM chart has 5 states Minimum number of MUX that are required to express a ...

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started