Answered step by step

Verified Expert Solution

Question

1 Approved Answer

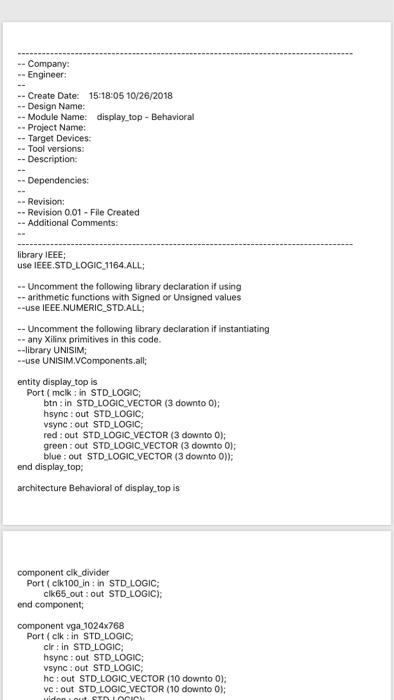

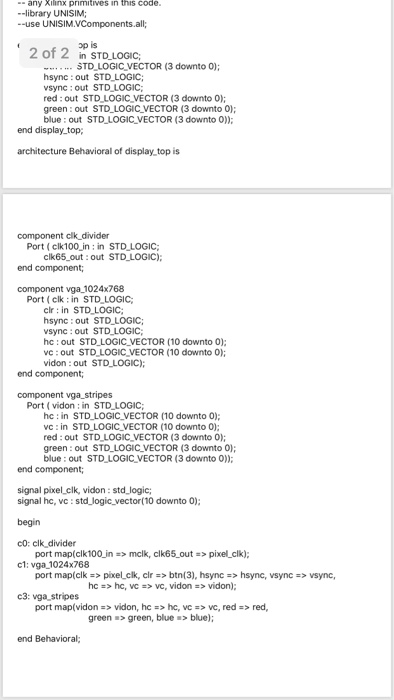

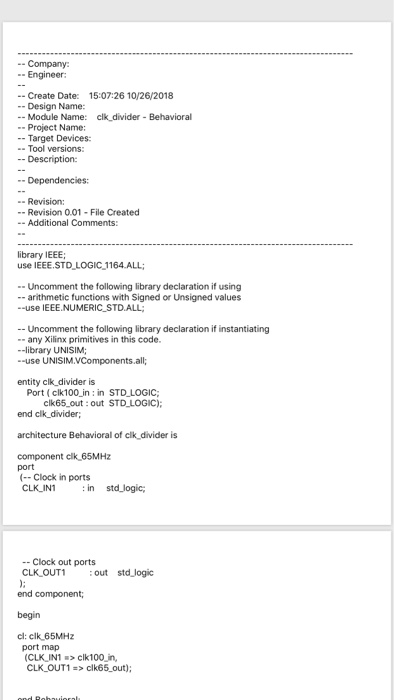

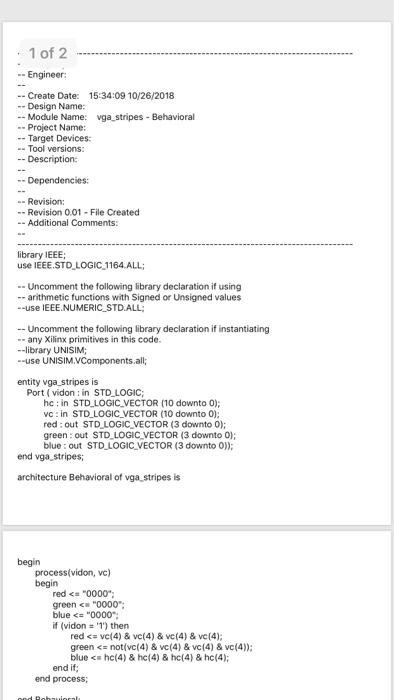

I have a code and the components for the code . This code generates a VGA output of stripes to a computer monitor . I

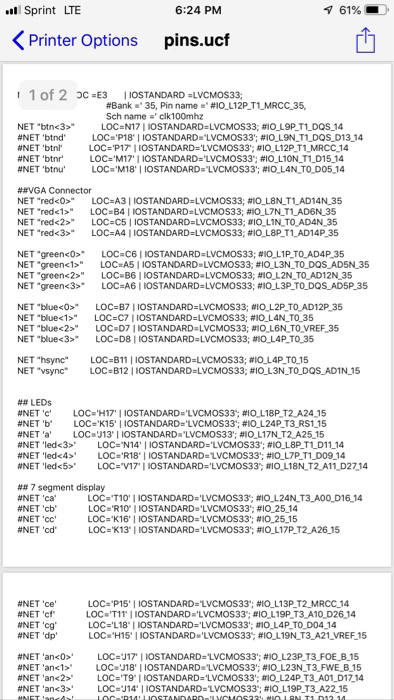

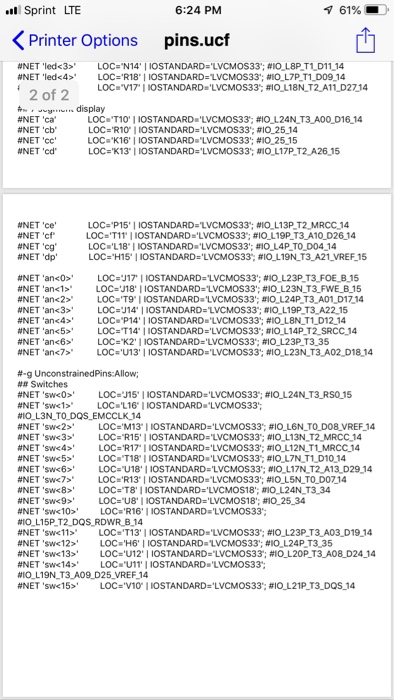

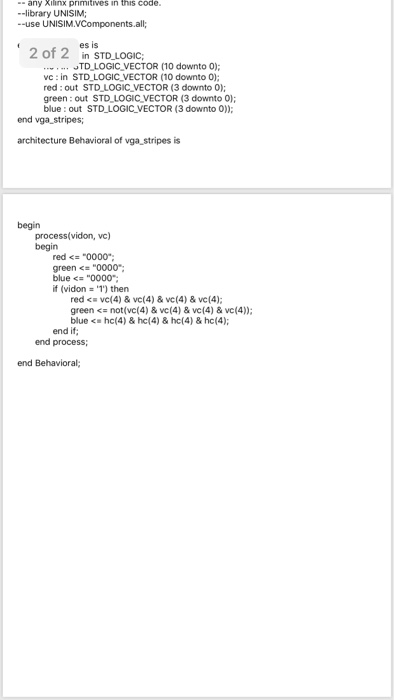

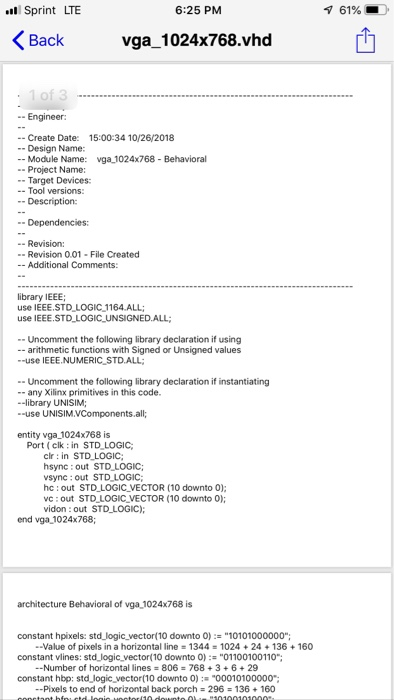

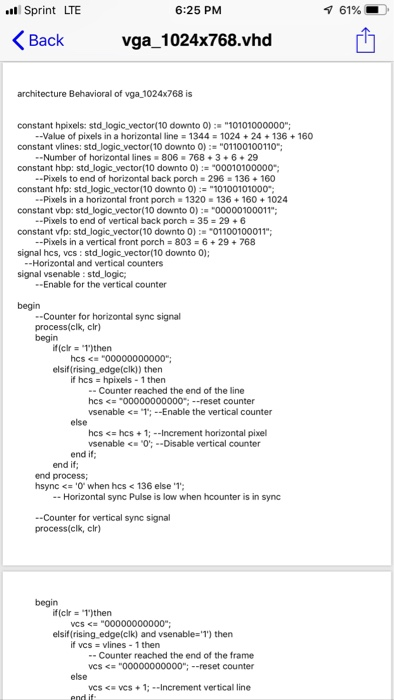

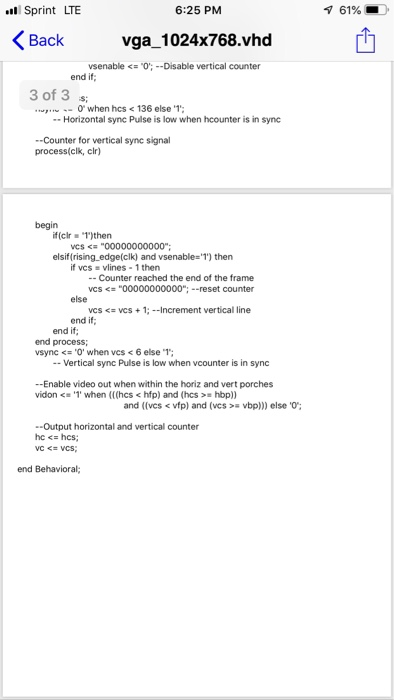

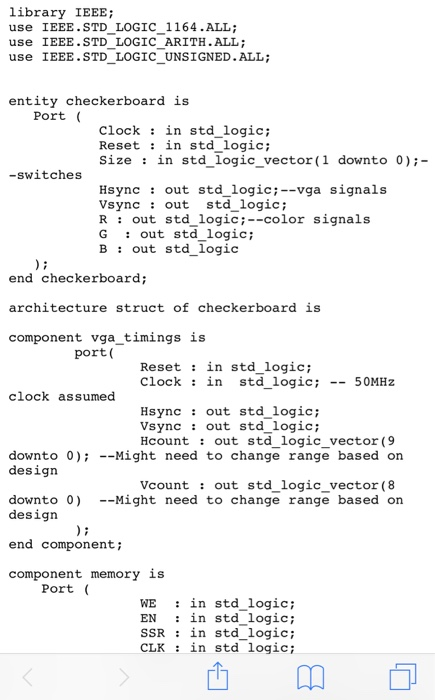

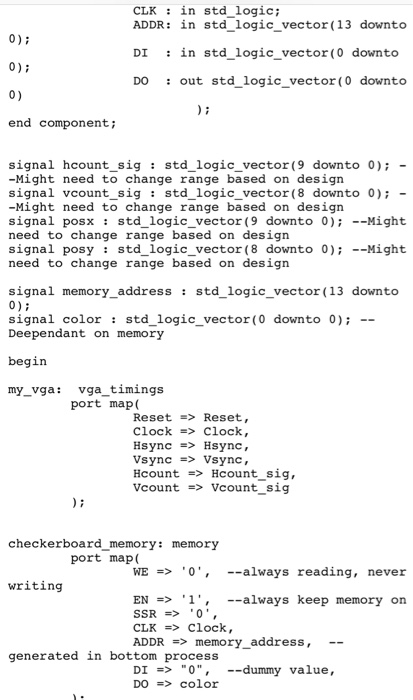

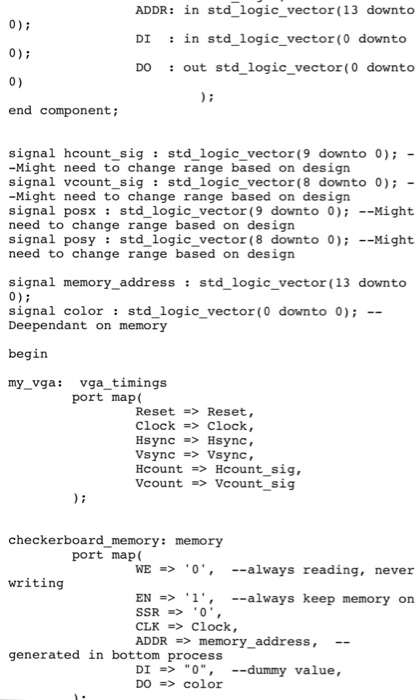

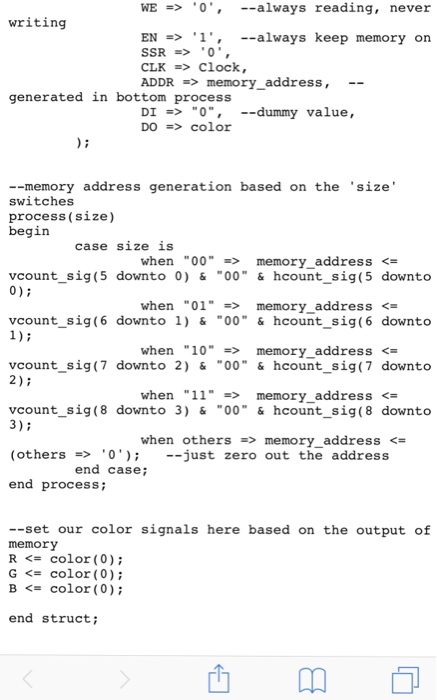

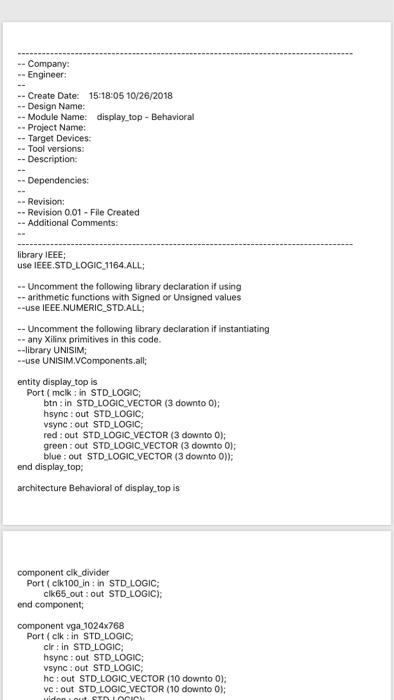

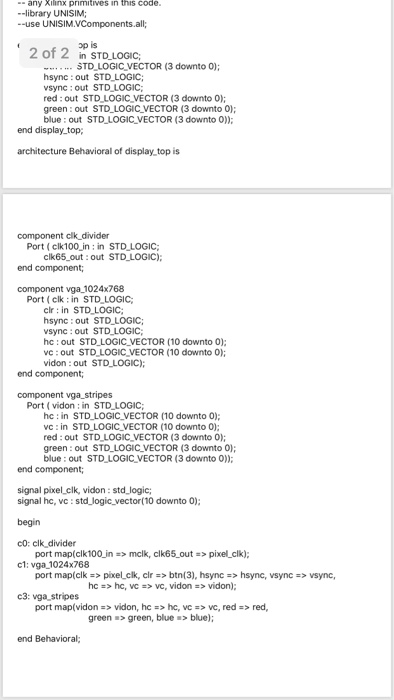

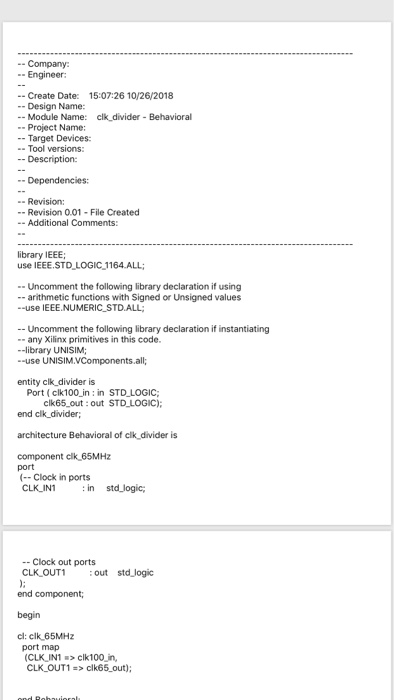

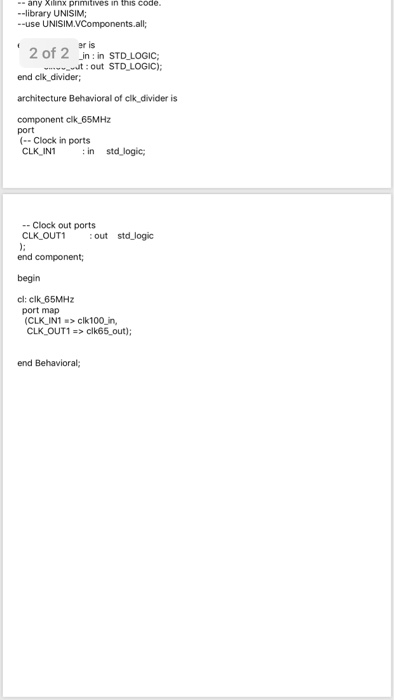

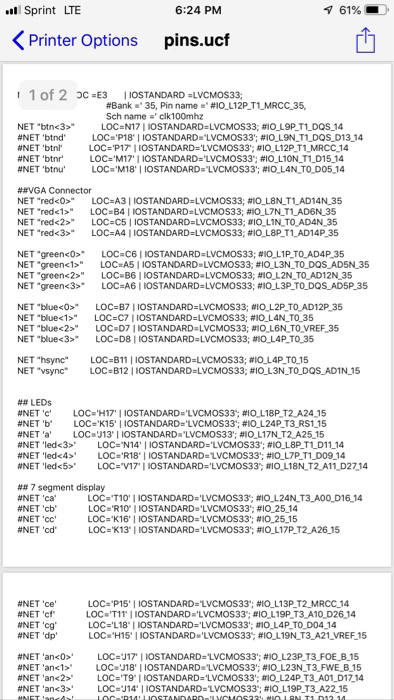

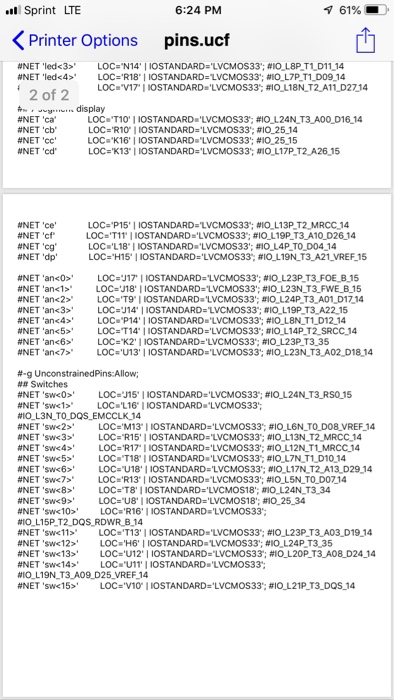

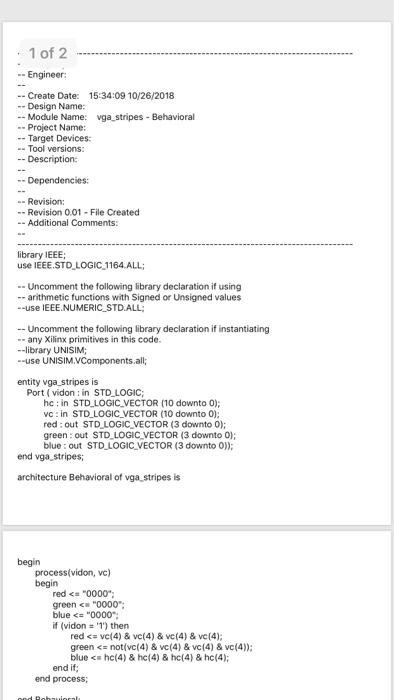

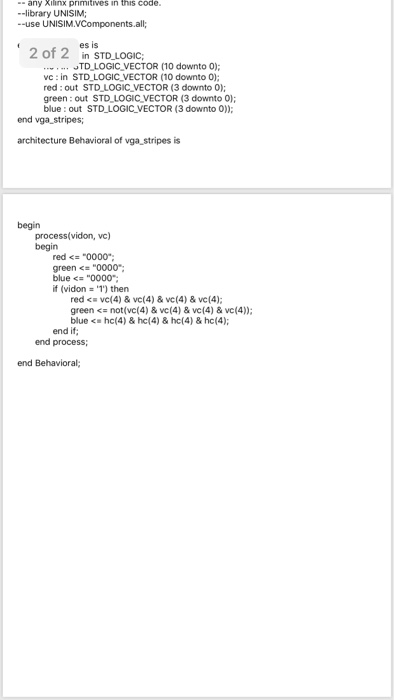

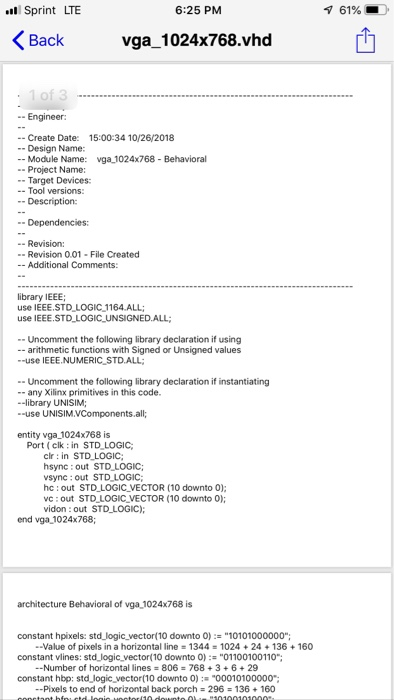

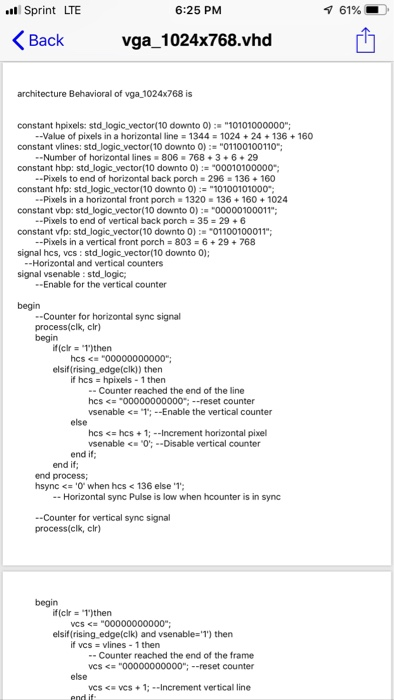

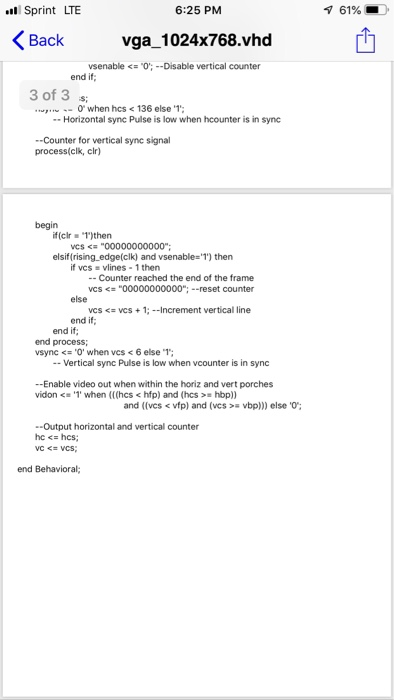

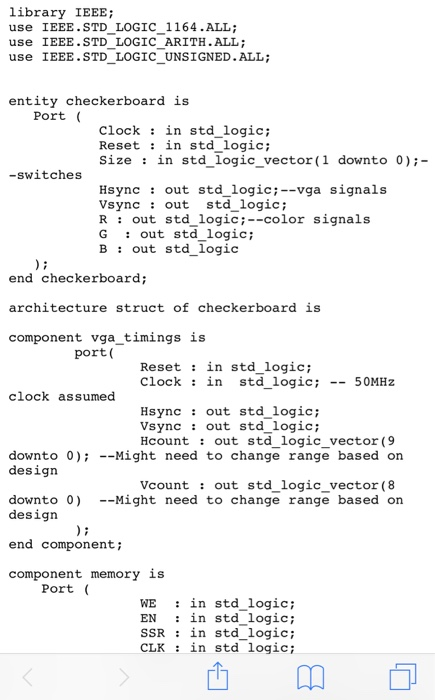

I have a code and the components for the code . This code generates a VGA output of stripes to a computer monitor . I also have a code that outputs a checkerboard pattern . Can someone adjust my original code using the checkerboard code to output a checkerboard pattern . I need the code for a Nexys 4 Artix-7 DDR board . I have also uploaded my pins file for the board as well .

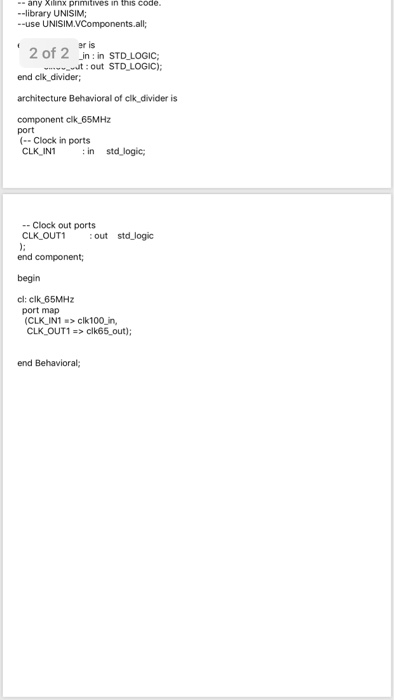

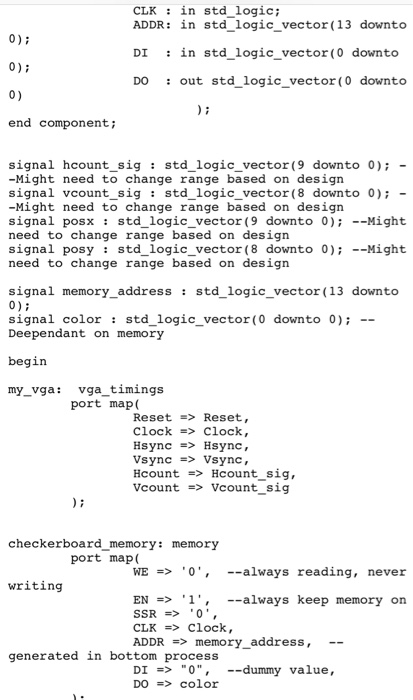

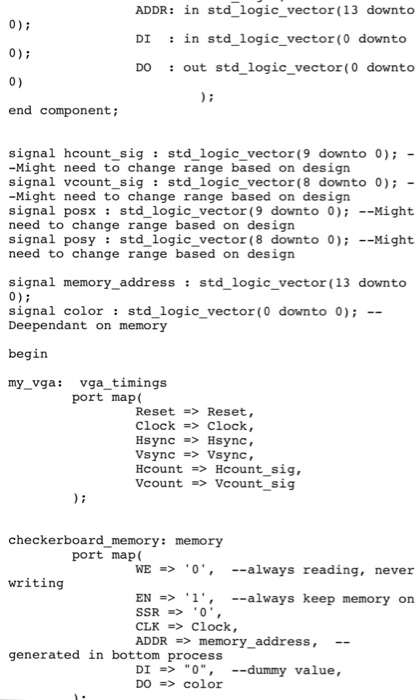

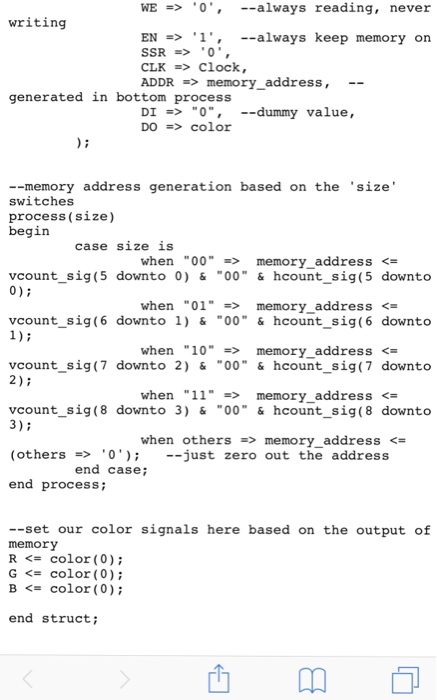

- Company Engineer - Create Date: 15:18:05 10/26/2018 Design Name: -Module Name: Project Name: Target Devices: - Tool versions: displaytop-Behavioral -Revision: -- Revision 0.01- File Created library IEEE use IEEE.STD LOGIC.1164.ALL Uncomment the following library declaration if using arithmetic functions with Signed or Unsigned values -use IEEE.NUMERIC STD.ALL; Uncomment the following library declaration if instantiating any Xilinx primitives in this code. --library UNISIM; -use UNISIM.VComponents.all; entity display top is Port (mclk: in STD LOGIC btn: in STD LOGIC VECTOR (3 downto 0); hsync: out STD LOGIC vsync: out STD LOGIC red:out STD LOGIC_VECTOR (3 downto O); green: out STD LOGIC VECTOR (3 downto 0); blue out STD LOGIC VECTOR (3 downto O)) end display top; architecture Behavioral of display top is component clk divider Port (clk100 in : in STD LOGIC end component; component vga 1024x768 clk65 out:out STD LOGIC); Port (clk: in STD LOGIC, clr: in STD LOGIC; hsync: out STD LOGIC; vsync: out STD LOGIC hc: out STD LOGIC VECTOR (10 downto 0); vc: out STD LOGIC VECTOR (10 downto O); - Company Engineer - Create Date: 15:18:05 10/26/2018 Design Name: -Module Name: Project Name: Target Devices: - Tool versions: displaytop-Behavioral -Revision: -- Revision 0.01- File Created library IEEE use IEEE.STD LOGIC.1164.ALL Uncomment the following library declaration if using arithmetic functions with Signed or Unsigned values -use IEEE.NUMERIC STD.ALL; Uncomment the following library declaration if instantiating any Xilinx primitives in this code. --library UNISIM; -use UNISIM.VComponents.all; entity display top is Port (mclk: in STD LOGIC btn: in STD LOGIC VECTOR (3 downto 0); hsync: out STD LOGIC vsync: out STD LOGIC red:out STD LOGIC_VECTOR (3 downto O); green: out STD LOGIC VECTOR (3 downto 0); blue out STD LOGIC VECTOR (3 downto O)) end display top; architecture Behavioral of display top is component clk divider Port (clk100 in : in STD LOGIC end component; component vga 1024x768 clk65 out:out STD LOGIC); Port (clk: in STD LOGIC, clr: in STD LOGIC; hsync: out STD LOGIC; vsync: out STD LOGIC hc: out STD LOGIC VECTOR (10 downto 0); vc: out STD LOGIC VECTOR (10 downto O)

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started