Question

I need help with VHDL coding I am asked to do this: I have created the design called fun. I have gates that are being

I need help with VHDL coding

I am asked to do this:

I have created the design called "fun". I have gates that are being used from my "gate_lib" which is a library of gates.

Here is my code:

library IEEE; use IEEE.std_logic_1164.all; use IEEE.numeric_std.all; library gate_lib;

entity FOUR_IN is port( A : in STD_LOGIC; B : in STD_LOGIC; C : in STD_LOGIC; D : in STD_LOGIC; F : out STD_LOGIC ); end FOUR_IN ;

--}} End of automatically maintained section

architecture structure of FOUR_IN is

component AND_GATE port(A, B: in bit; F out bit); end component;

component OR_GATE port(A, B: in bit; F out bit); end component;

component NAND_GATE port(A, B: in bit; F out bit); end component;

component NOR_GATE port(A, B: in bit; F out bit); end component;

component XNOR_GATE port(A, B: in bit; F out bit); end component;

component XOR_GATE port(A, B: in bit; F out bit); end component;

component NOT_GATE port(X: in std_logic; Z: out bit); end component;

signal A, B, C, D, X, Z: bit;

end structure ; --begin ---- process(A,B,C,D) ---- begin ---- F

THIS IS MY QUESTION: How should I input the logic function part "F(A,B,C,D)=...."?

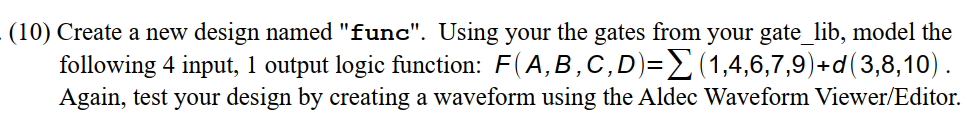

(10) Create a new design named "func". Using your the gates from your gate_lib, model the following 4 input,1 output logic function: F(A,B,C,D)2 (1,4,6,7,9)+d(3,8,10) Again, test your design by creating a waveform using the Aldec Waveform Viewer/EditorStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started