Answered step by step

Verified Expert Solution

Question

1 Approved Answer

I really dont understand this. Can someone draw it please? For the following three questions, you will be designing a memory subsystem for a computer

I really dont understand this. Can someone draw it please?

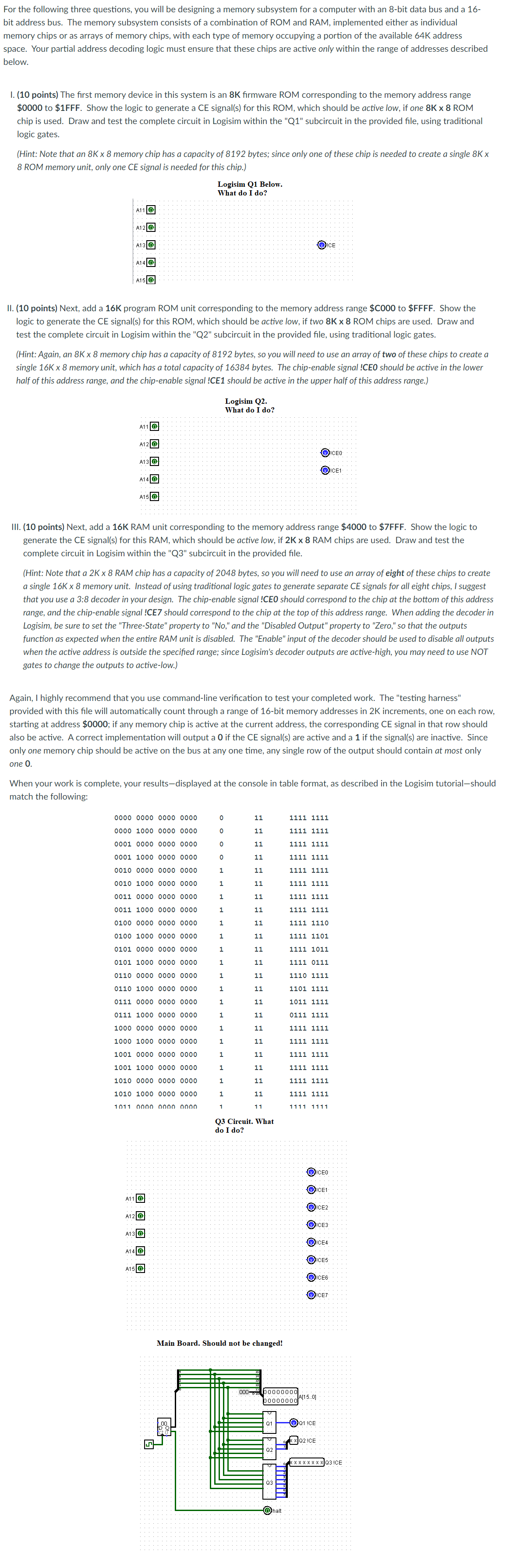

For the following three questions, you will be designing a memory subsystem for a computer with an bit data bus and a bit address bus. The memory subsystem consists of a combination of ROM and RAM, implemented either as individual memory chips or as arrays of memory chips, with each type of memory occupying a portion of the available addres space. Your partial address decoding logic must ensure that these chips are active only within the range of addresses described below.

I. points The first memory device in this system is an firmware ROM corresponding to the memory address range $ to $ Show the logic to generate a CE signals for this ROM, which should be active low, if one x ROM chip is used. Draw and test the complete circuit in Logisim within the Q subcircuit in the provided file, using traditional logic gates.

Hint: Note that an x memory chip has a capacity of bytes; since only one of these chip is needed to create a single ROM memory unit, only one CE signal is needed for this chip.

Logisim Q Below What do I do

II points Next, add a program ROM unit corresponding to the memory address range $ to $ Show the logic to generate the CE signals for this ROM, which should be active low, if two ROM chips are used. Draw and test the complete circuit in Logisim within the Q subcircuit in the provided file, using traditional logic gates.

Hint: Again, an K memory chip has a capacity of bytes, so you will need to use an array of two of these chips to create a single x memory unit, which has a total capacity of bytes. The chipenable signal CEO should be active in the lower half of this address range, and the chipenable signal CE should be active in the upper half of this address range.

Logisim Q What do I do

A

A

A

OICEO

A

OCE

A

III. points Next, add a K RAM unit corresponding to the memory address range $ to $ Show the logic to generate the CE signals for this RAM, which should be active low, if RAM chips are used. Draw and test the complete circuit in Logisim within the Q subcircuit in the provided file.

Hint: Note that a RAM chip has a capacity of bytes, so you will need to use an array of eight of these chips to create a single memory unit. Instead of using traditional logic gates to generate separate CE signals for all eight chips, I suggest that you use a : decoder in your design. The chipenable signal CEO should correspond to the chip at the bottom of this addres range, and the chipenable signal CE should correspond to the chip at the top of this address range. When adding the decoder in Logisim, be sure to set the "ThreeState" property to No and the "Disabled Output" property to "Zero," so that the outputs function a sexpected when the e entire RAM unit is disabled. The "Enable" input of the decoder should be used to disable all outputs when the active address is outside the specifed range; since Logisis's decoder outputs are activehigh, you may need to use NOT gates to change the outputs to activeow

Again, I highly recommend that you use commandline verification to test your completed work. The "testing harness provided with this file will automatically count through a range of bit memory addresses in increments, one on each row, starting at address $; if any memory chip is active at the current address, the corresponding CE signal in that row should also be active. A correct implementation will output a if the signals are active and a if the signals are inactive. Since only one memory chip should be active on the bus at any one time, any single row of the output should contain at most only one

When your work is complete, your resultsdisplayed at the console in table format, as described in the Logisim tutorialshould match the following:

Main Board. Should not be changed:

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started