Answered step by step

Verified Expert Solution

Question

1 Approved Answer

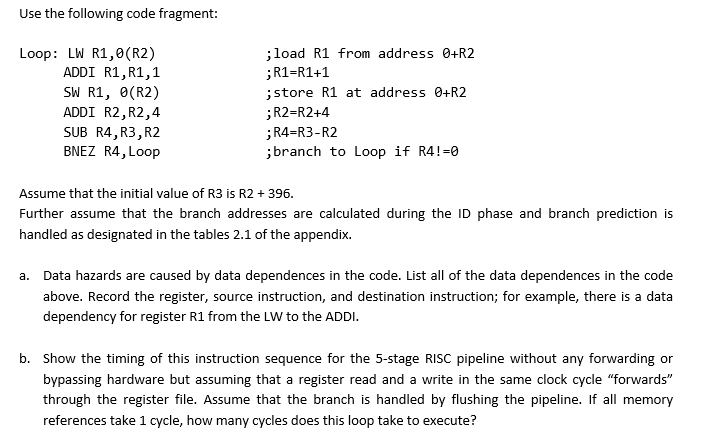

IN MIPS ASSMEBLY Use the following code fragment Loop: LW R1,0(R2) ADDI R1,R1,1 SW R1, 0(R2) ADDI R2,R2,4 SUB R4,R3,R2 BNEZ R4, Loop ;load R1

IN MIPS ASSMEBLY

Use the following code fragment Loop: LW R1,0(R2) ADDI R1,R1,1 SW R1, 0(R2) ADDI R2,R2,4 SUB R4,R3,R2 BNEZ R4, Loop ;load R1 from address 0+R2 R1-R1+1 store R1 at address 0+ ;R2-R2+4 ;R4-R3-R2 ,branch to Loop if R41-e Assume that the initial value of R3 is R2396 Further assume that the branch addresses are calculated during the ID phase and branch prediction is handled as designated in the tables 2.1 of the appendix. a. Data hazards are caused by data dependences in the code. List all of the data dependences in the code above. Record the register, source instruction, and destination instruction; for example, there is a data dependency for register R1 from the LW to the ADDI b. Show the timing of this instruction sequence for the 5-stage RISC pipeline without any forwarding or bypassing hardware but assuming that a register read and a write in the same clock cycle "forwards" through the register file. Assume that the branch is handled by flushing the pipeline. If all memory references take 1 cycle, how many cycles does this loop take to executeStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started