Question

In this Assignment you will use the Data Path Designed In-Class to carry-out the capture and subtraction of two number using the Two's Complement subtraction

In this Assignment you will use the Data Path Designed In-Class to carry-out the capture and subtraction of two number using the Two's Complement subtraction algorithm.

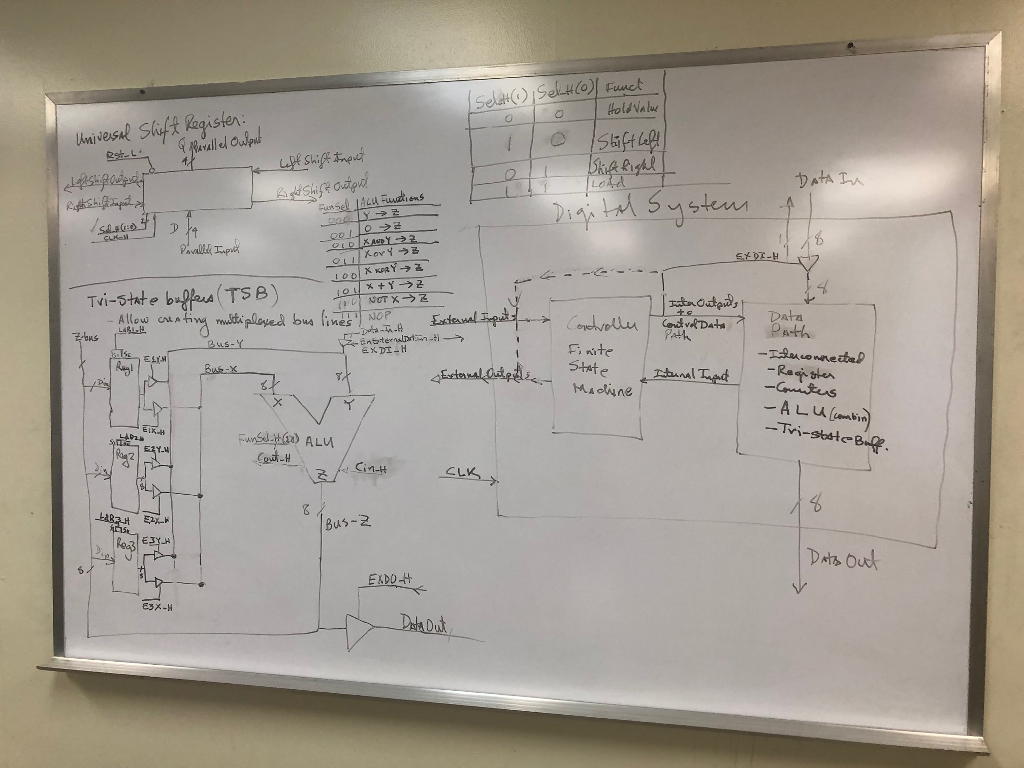

The Data Path has an Arithmetic and Logic Unit (ALU) connected to three (1) Registers (R1, R2, R3).

The Registers OUPUTS each connects through Tri-state buffers to either of two Data Busses (X bus, or Y bus),

these busses are also connected to the X-input and Y-input of the ALU, these allow your Data Path Controller to send the

outputs from two of the Registers to either the X input or Y input of the ALU simultaneously which also controlling the three (3) ALU FuncSel_H(2:0) inputs of the ALU.

The Registers (R1, R2, R3) INPUTS are (all three) connected to the Z-Bus that comes from the ALU Output, this will allow loading the output of the ALU into any of the Registers.

Besides the outputs of the Registers, an external Data Input (Din_H) can be enabled into the Y-Bus through Tri-State Buffers, these buffers are enabled by control signal EXDI_H, which is also sent as an Output signal that indicates to an external entity to drive a new external data value into the Din_H external inputs.

Besides the inputs of the Register, and external Data Output (Dout_H) can receive the output from the Z-Bus through Tri-State Buffers, these buffers are enabled by a control signal EXDO_H, which is also an output signal (renamed as DONE_H) that indicates to an external entity that the value resulting from having subtracted (R1 - R2) and which has been stored in R3, that such value is being driven into the Dout_H external output.

For this assignment you are to complete the following artifacts:

- VHDL Model for the ALU:

This model has two data inputs (X-bus, Y-bus), one Result Output ( Z-Bus), an input carry (Cin_H), and output carry (Cout_H), and three (3) function selection (FuncSel_H(2:0) control inputs. You can implement the 7 functions and the No-Op eight function, using either a structured model with Equations or a behaviour model using VHDL operations.

- VHDL Model for the Data Path:

This model must include the three (3) registers (R1, R2, R3) using the Universal Shift Register Model, with input control signals for loading each Register (LdR1_H, LdR2_H, LdR3_H) from the Z-Bus, all three RegRst_L. inputs should be connected to a common SysRst_L signal. It must also include two sets of Tri-State buffers on the Output of each Register, these Tri-State buffers are for selectively connecting each Register Output to either the X-Bus or to the Y-Bus.

- VHDL Model for the Data Path FSM Controller:

The Block diagram and the State Transition diagram were developed in class. You can use the Vivado generic model for a Moore FSM .

- VHDL Model for the complete Digital System for Two's Complement subtraction:

This model should declare, instantiate, and interconnect the Data Path VHDL model and the FSM Controller VHDL models.

- VHDL for Test Bench Model for the Complete Digital System:

Your Test Cases provide the first input (to be loaded into R1), the second input (to be loaded into R2), and then checks the result with an Assert statement about the Difference value that comes out of the Dout_H external output. you must provide at least two test cases, one with two(R1,R2) numbers less than 8 and two with two (R1, R2) numbers larger than 8.

ulldO Fwat ens EtDE NOP Ata a-th State nl Ted Bus-2 6 ulldO Fwat ens EtDE NOP Ata a-th State nl Ted Bus-2 6

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started