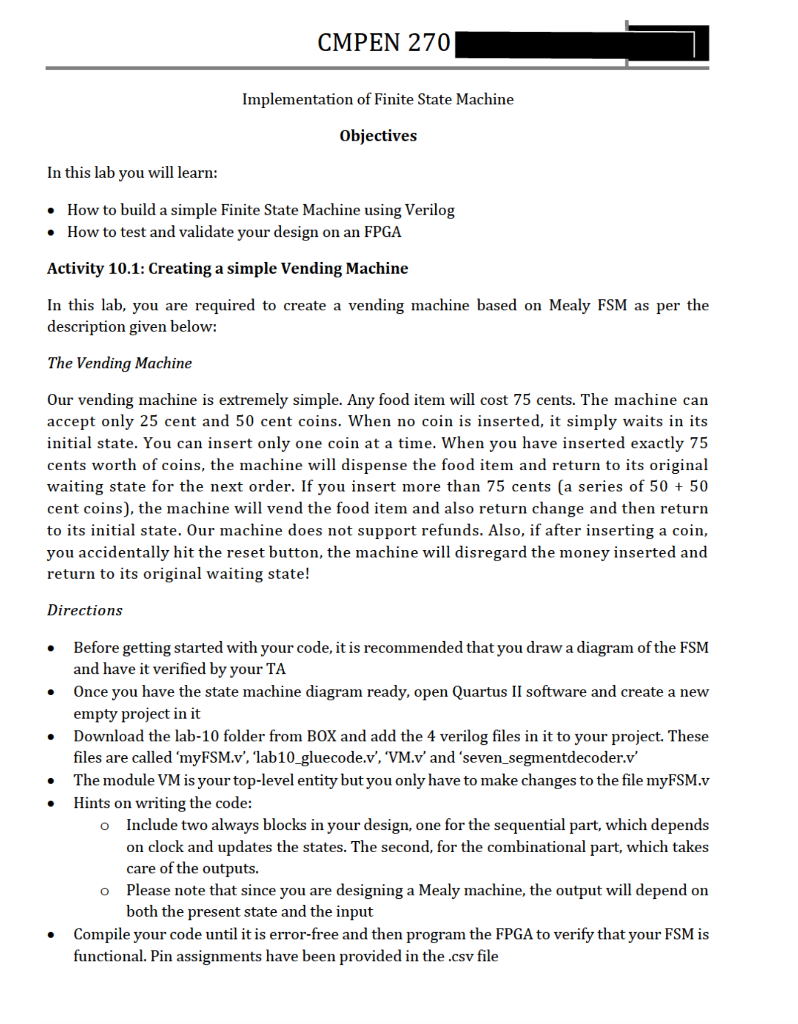

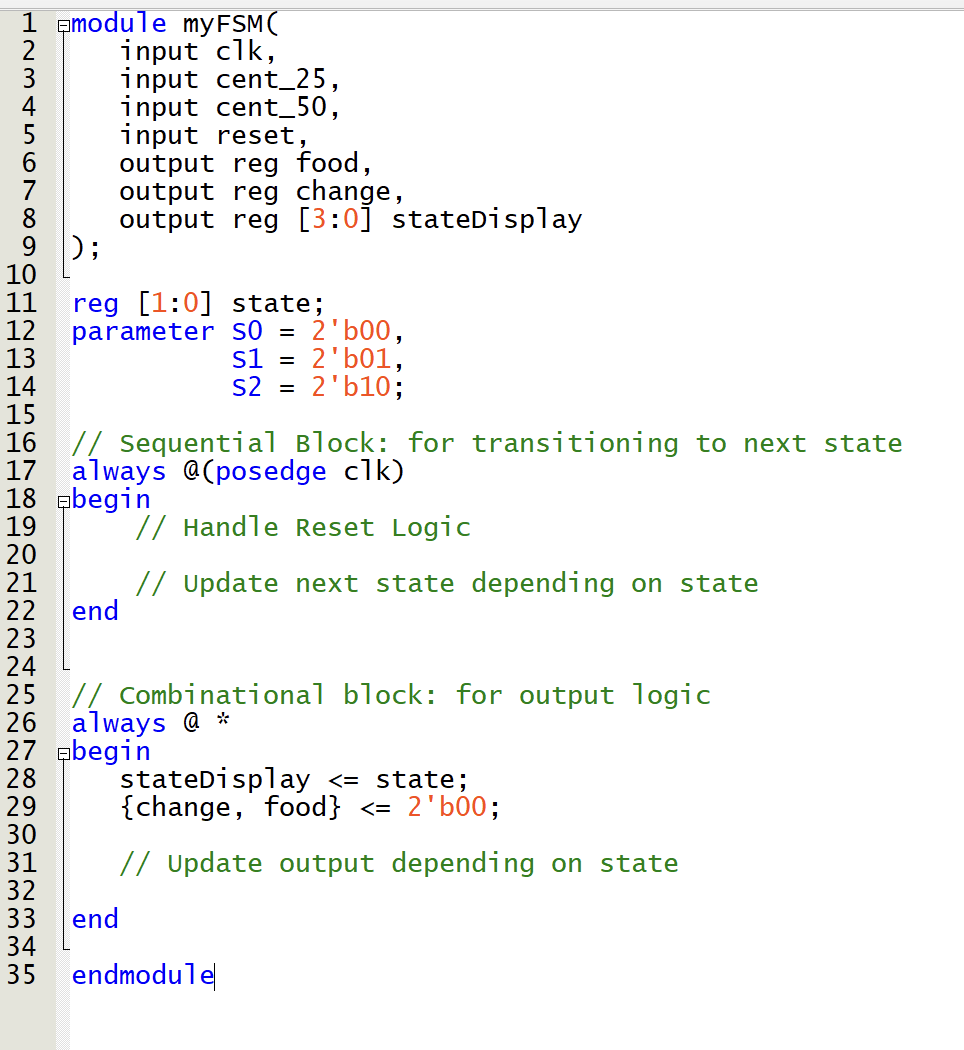

In this lab you will learn: - How to build a simple Finite State Machine using Verilog - How to test and validate your design on an FPGA Activity 10.1: Creating a simple Vending Machine In this lab, you are required to create a vending machine based on Mealy FSM as per the description given below: The Vending Machine Our vending machine is extremely simple. Any food item will cost 75 cents. The machine can accept only 25 cent and 50 cent coins. When no coin is inserted, it simply waits in its initial state. You can insert only one coin at a time. When you have inserted exactly 75 cents worth of coins, the machine will dispense the food item and return to its original waiting state for the next order. If you insert more than 75 cents (a series of 50+50 cent coins), the machine will vend the food item and also return change and then return to its initial state. Our machine does not support refunds. Also, if after inserting a coin, you accidentally hit the reset button, the machine will disregard the money inserted and return to its original waiting state! Directions - Before getting started with your code, it is recommended that you draw a diagram of the FSM and have it verified by your TA - Once you have the state machine diagram ready, open Quartus II software and create a new empty project in it - Download the lab-10 folder from BOX and add the 4 verilog files in it to your project. These files are called 'myFSM.v', 'lab10_gluecode.v', 'VM.v' and 'seven_segmentdecoder.v' - The module VM is your top-level entity but you only have to make changes to the file myFSM.v - Hints on writing the code: o Include two always blocks in your design, one for the sequential part, which depends on clock and updates the states. The second, for the combinational part, which takes care of the outputs. - Please note that since you are designing a Mealy machine, the output will depend on both the present state and the input - Compile your code until it is error-free and then program the FPGA to verify that your FSM is functional. Pin assignments have been provided in the .csv file // Sequentia 1 Block: for transitioning to next state a7ways @(posedge c7k) abegin // Handle Reset Logic end // Combinationa] block: for output logic always a * abegin statedisplay