Question

In VHDL language, design a generic ALU circuit with the giving code. You will design an Arithmetic Logic Unit (ALU) thatis capable of carrying out

In VHDL language, design a generic ALU circuit with the giving code.

You will design an Arithmetic Logic Unit (ALU) thatis capable of carrying out several important operations including addition, logical operations and branchingoperations.

You are required to design an ALU, which can takepart in the following operations: 1.Unsigned additionof 16-bit numbers.2. 2s complement addition/subtractionof 16-bit numbers. 3. Logicaland 4. Logicalor 5. Logicalxor 6.Set on less than 7.Branch if equal

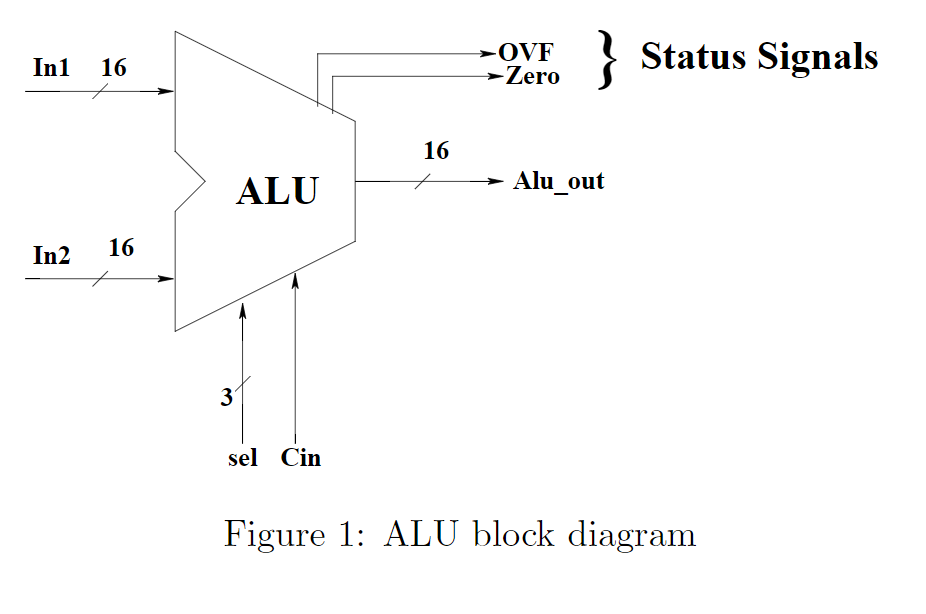

in addition to the result produced by the ALU, the branch equal (beq) operation should generate a controloutput (zero) that indicates if operand In1 is equal to operand In2. Your ALU design should also provide fora 2s complement overflow indicator. The block diagram of this ALU is shown Figure 1.

entity ALU is

generic (

Dwidth : integer := 16);

port (

In1, In2 : in std_logic_vector(Dwidth-1 downto 0);

Alu_out : out std_logic_vector(Dwidth-1 downto 0);

sel : in std_logic_vector (2 downto 0);

Cin : in std_logic;

zero, OVF : out std_logic);

end ALU;

Notice that there is no clock signal used in this component. This ALU is a pure combinational circuit,unlike the sequential Memory and Register File designs. TheIn1, In2 inputs and the Aluout outputrepresent the two data inputs and one data output of the ALU. TheCinrepresents the carry in to theALU. The branch equal comparison indicator zero is alwaysset to one whenIn1 =In2. The OVF bit isasserted when the add or subtract operations generate an overflow, as defined in standard 2s complementbased operations. Finally,selis a vector of three control bits that select the operation the ALU will perform.Use the encoding shown in Table 1 for the control inputs.

Table 1:

ALU control line ----Function

000 --------------------and

001 --------------------or

010 -------------------unsigned add

011 --------------------xor

100 -------------------signed add

101 -------------------signed subtract

110 ---------------------set on less than

111 --------------------beq

1.Please complete the ALU design as specified. You must design and implement both behavioral and

structural description here.

For behavioral description, you can use case statements to model the various operations performed

by the ALU.

For structural description, implement a single bit ALU that performs the desired operations from Table 1 and instantiate these in ripple-carry fashion to implement your N-bit ALU. Appendix C of the Hennessy and Paterson textbook (Computer Organization and Design) contains informatiON on implementing a similar ALU from a cascade of 1-bit ALUs.

Take note of the signed and unsigned operations to be performed here. They can be done by casting the

std_logic_vector signals as signed or unsigned. This functionality comes from your IEEE.STD libraries.

Please keep IEEE.STD_LOGIC_UNSIGNED declared by default to maintain interoperability with the simulator, and cast signed operation inputs as required.

2.Simulate your ALU while demonstrating examples of all required operations, including signed and un-signed verification.

Show transcribed image text

rStatus Signals Inl 16 Zero 16 Alu out ALU In2 16 sel Cin Figure 1: ALU block diagram rStatus Signals Inl 16 Zero 16 Alu out ALU In2 16 sel Cin Figure 1: ALU block diagramStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started