Question

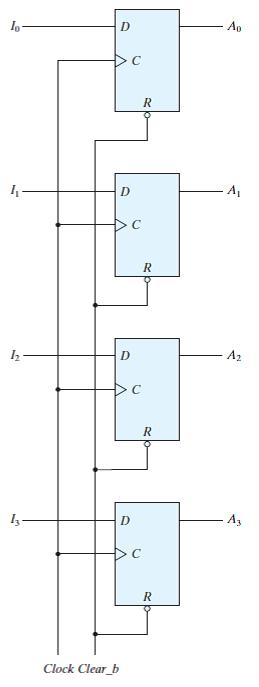

Include a 2-input NAND gate in the register of Fig. 6.1 and connect the gate output to the C inputs of all the flip-flops. One

Include a 2-input NAND gate in the register of Fig. 6.1 and connect the gate output to the C inputs of all the flip-flops. One input of the NAND gate receives the clock pulses from the clock generator, and the other input of the NAND gate provides a parallel load control. Explain the operation of the modified register. Explain why this circuit might have operational problems.

Include a 2-input NAND gate in the register of Fig. 6.1 and connect the gate output to the C inputs of all the flip-flops. One input of the NAND gate receives the clock pulses from the clock generator, and the other input of the NAND gate provides a parallel load control. Explain the operation of the modified register. Explain why this circuit might have operational problems. Ap A, A2 Clock Clear_b

Step by Step Solution

3.45 Rating (165 Votes )

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Vector Mechanics for Engineers Statics and Dynamics

Authors: Ferdinand Beer, E. Russell Johnston, Jr., Elliot Eisenberg, William Clausen, David Mazurek, Phillip Cornwell

8th Edition

73212229, 978-0073212227

Students also viewed these Electrical Engineering questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App