Answered step by step

Verified Expert Solution

Question

1 Approved Answer

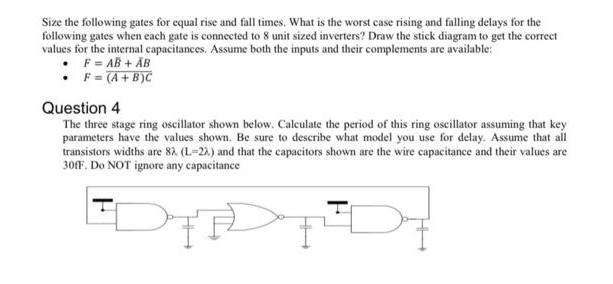

Size the following gates for equal rise and fall times. What is the worst case rising and falling delays for the following gates when

Size the following gates for equal rise and fall times. What is the worst case rising and falling delays for the following gates when each gate is connected to 8 unit sized inverters? Draw the stick diagram to get the correct values for the internal capacitances. Assume both the inputs and their complements are available: F = AB + AB F = (A + B)C Question 4 The three stage ring oscillator shown below. Calculate the period of this ring oscillator assuming that key parameters have the values shown. Be sure to describe what model you use for delay. Assume that all transistors widths are 82 (L-22.) and that the capacitors shown are the wire capacitance and their values are 30fF. Do NOT ignore any capacitance PTT 27

Step by Step Solution

★★★★★

3.43 Rating (153 Votes )

There are 3 Steps involved in it

Step: 1

Question 3 To size the gates for equal rise and fall times we need to ensure that the pullup and pulldown networks of each gate have equal resistance We can start by drawing the stick diagram for each ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started