Answered step by step

Verified Expert Solution

Question

1 Approved Answer

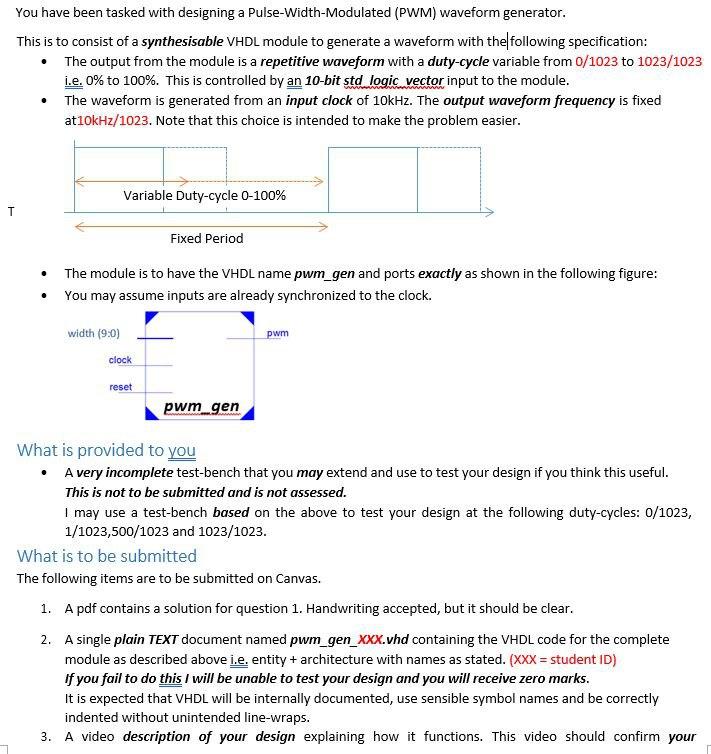

You have been tasked with designing a Pulse-Width-Modulated (PWM) waveform generator. This is to consist of a synthesisable VHDL module to generate a waveform

You have been tasked with designing a Pulse-Width-Modulated (PWM) waveform generator. This is to consist of a synthesisable VHDL module to generate a waveform with the following specification: The output from the module is a repetitive waveform with a duty-cycle variable from 0/1023 to 1023/1023 i.e. 0% to 100%. This is controlled by an 10-bit std logic vector input to the module. The waveform is generated from an input clock of 10kHz. The output waveform frequency is fixed at10kHz/1023. Note that this choice is intended to make the problem easier. Variable Duty-cycle 0-100% Fixed Period The module is to have the VHDL name pwm_gen and ports exactly as shown in the following figure: You may assume inputs are already synchronized to the clock. width (9:0) pwm clock reset pwm_gen What is provided to you A very incomplete test-bench that you may extend and use to test your design if you think this useful. This is not to be submitted and is not assessed. I may use a test-bench based on the above to test your design at the following duty-cycles: 0/1023, 1/1023,500/1023 and 1023/1023. What is to be submitted The following items are to be submitted on Canvas. 1. A pdf contains a solution for question 1. Handwriting accepted, but it should be clear. 2. A single plain TEXT document named pwm_gen_XXX.vhd containing the VHDL code for the complete module as described above i.e, entity + architecture with names as stated. (XXX = student ID) If you fail to do this I will be unable to test your design and you will receive zero marks. It is expected that VHDL will be internally documented, use sensible symbol names and be correctly indented without unintended line-wraps. 3. A video description of your design explaining how it functions. This video should confirm your

Step by Step Solution

★★★★★

3.38 Rating (151 Votes )

There are 3 Steps involved in it

Step: 1

LIBRARY IEEE USE IEEESTDLOGIC1164ALL use ieeenumericstdall USE IEEESTDLOGICU...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started