Question: Lab Instructions and Objectives: 1. Download and install Simulator 7-5-50.exe on your Microsoft Windows Operating System machine. 2. Follow the instruction as stated in

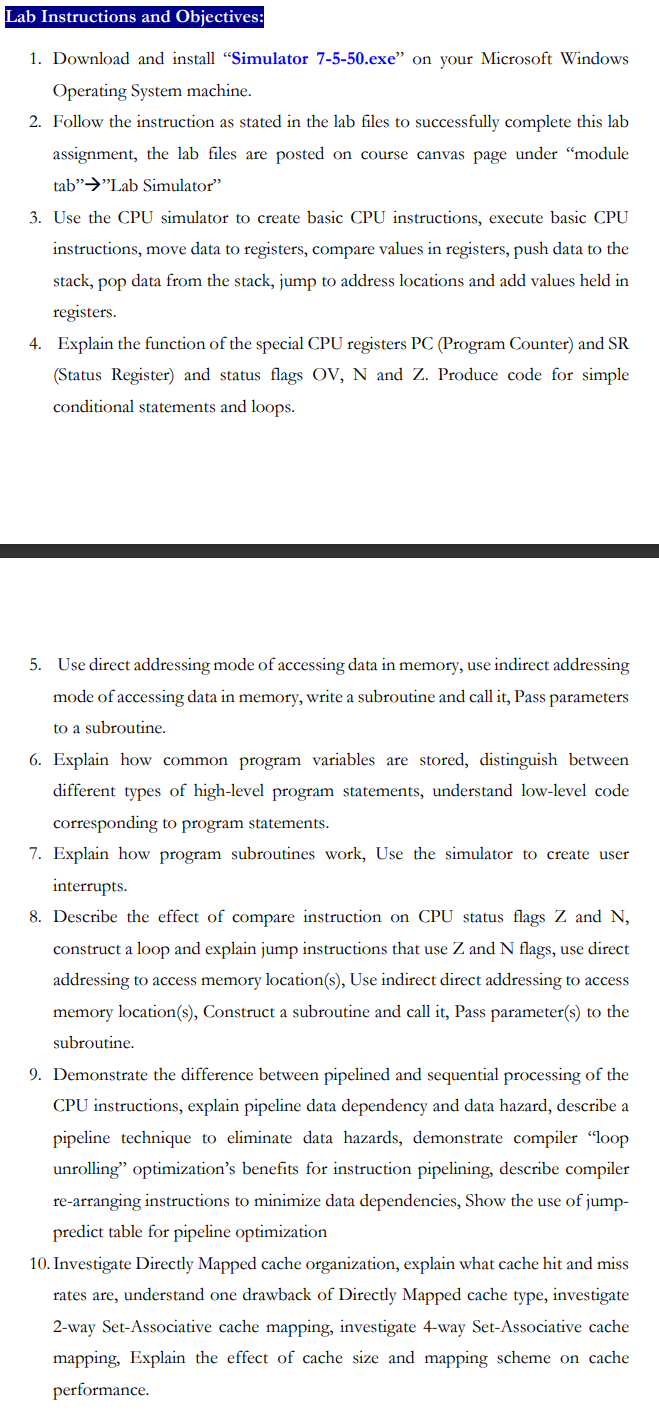

Lab Instructions and Objectives: 1. Download and install Simulator 7-5-50.exe" on your Microsoft Windows Operating System machine. 2. Follow the instruction as stated in the lab files to successfully complete this lab assignment, the lab files are posted on course canvas page under module tab""Lab Simulator" 3. Use the CPU simulator to create basic CPU instructions, execute basic CPU instructions, move data to registers, compare values in registers, push data to the stack, pop data from the stack, jump to address locations and add values held in registers. 4. Explain the function of the special CPU registers PC (Program Counter) and SR (Status Register) and status flags OV, N and Z. Produce code for simple conditional statements and loops. 5. Use direct addressing mode of accessing data in memory, use indirect addressing mode of accessing data in memory, write a subroutine and call it, Pass parameters to a subroutine. 6. Explain how common program variables are stored, distinguish between different types of high-level program statements, understand low-level code corresponding to program statements. 7. Explain how program subroutines work, Use the simulator to create user interrupts. 8. Describe the effect of compare instruction on CPU status flags Z and N, construct a loop and explain jump instructions that use Z and N flags, use direct addressing to access memory location(s), Use indirect direct addressing to access memory location(s), Construct a subroutine and call it, Pass parameter(s) to the subroutine. 9. Demonstrate the difference between pipelined and sequential processing of the CPU instructions, explain pipeline data dependency and data hazard, describe a pipeline technique to eliminate data hazards, demonstrate compiler "loop unrolling" optimization's benefits for instruction pipelining, describe compiler re-arranging instructions to minimize data dependencies, Show the use of jump- predict table for pipeline optimization 10. Investigate Directly Mapped cache organization, explain what cache hit and miss rates are, understand one drawback of Directly Mapped cache type, investigate 2-way Set-Associative cache mapping, investigate 4-way Set-Associative cache mapping, Explain the effect of cache size and mapping scheme on cache performance.

Step by Step Solution

3.49 Rating (166 Votes )

There are 3 Steps involved in it

Solutions Step 1 Explanation understanding CPU registers and status flags memory addressing modes subroutines interrupts and cache organization These ... View full answer

Get step-by-step solutions from verified subject matter experts