Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Many SMP (Symmetric multiprocessing) systems have different level of caches; one level is local to each processing core, and another level is shared among

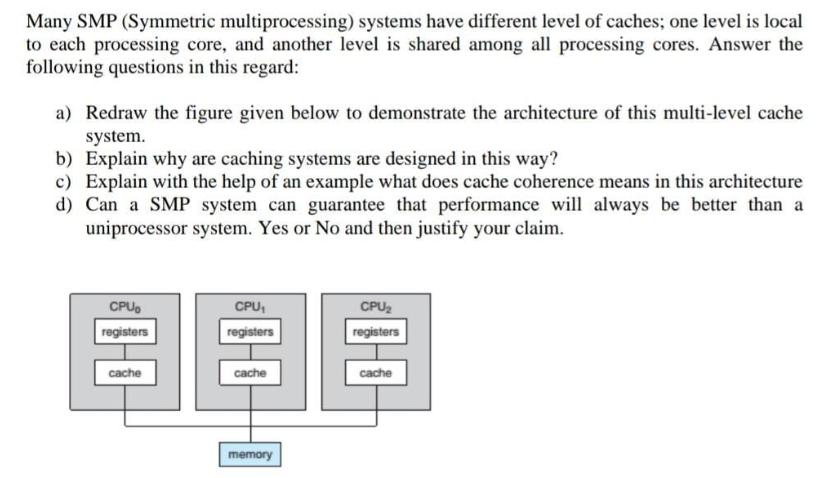

Many SMP (Symmetric multiprocessing) systems have different level of caches; one level is local to each processing core, and another level is shared among all processing cores. Answer the following questions in this regard: a) Redraw the figure given below to demonstrate the architecture of this multi-level cache system. b) Explain why are caching systems are designed in this way? c) Explain with the help of an example what does cache coherence means in this architecture d) Can a SMP system can guarantee that performance will always be better than a uniprocessor system. Yes or No and then justify your claim. CPU registers cache CPU registers cache memory CPU registers cache

Step by Step Solution

★★★★★

3.40 Rating (162 Votes )

There are 3 Steps involved in it

Step: 1

a All the processors in the symmetric multiprocessing architecture contain a common bus and main ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started