Answered step by step

Verified Expert Solution

Question

1 Approved Answer

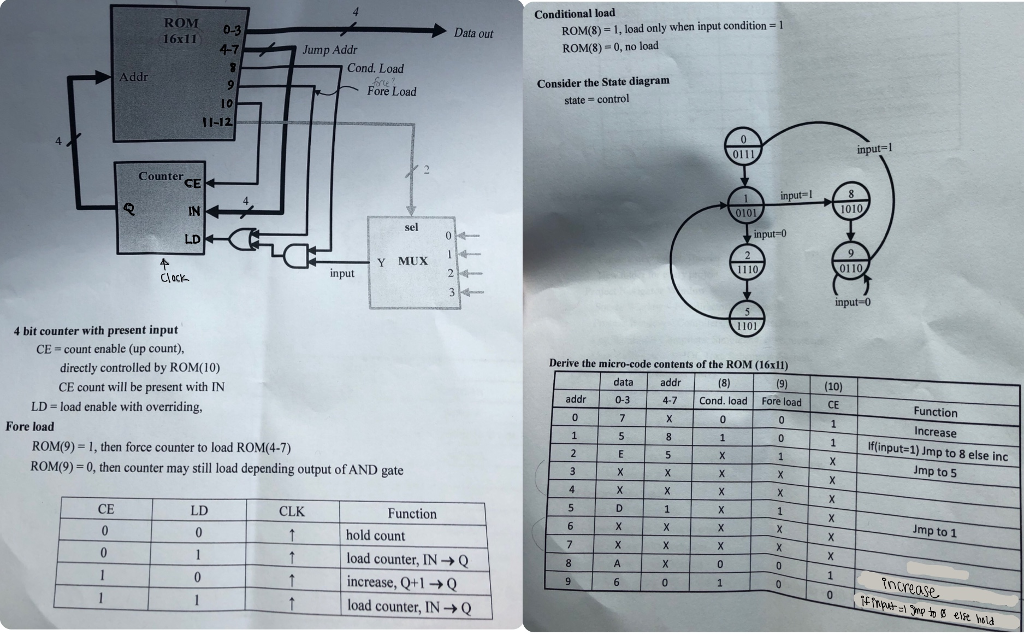

MICROPROGRAMMABLE CONTROL USING XILYNX. ONLY SOLVE IF YOU KNOW VHDL IMPLEMENTATION OF FPGAS USING XILYNX. USING XILYNX, DESIGN THE ROM, COUNTER, AND MUX AND SHOW

MICROPROGRAMMABLE CONTROL USING XILYNX. ONLY SOLVE IF YOU KNOW VHDL IMPLEMENTATION OF FPGAS USING XILYNX.

USING XILYNX, DESIGN THE ROM, COUNTER, AND MUX AND SHOW A STEP BY STEP EXPLANATION OF GETTING:

1. TOP LEVEL SCHEMATIC

2. STATE DIAGRAM FOR MICROCODE

3. MICROCODE WITH COMMENTS

4. WAVEFORM AND VERIFICATION

**DESCRIBE EVERY CRITICAL WINDOW IN THE SIMULATION TO VERIFY THE RESULTS

ONLY IF YOUR RESULT IS CORRECT AND PROVIDES EXPLANATIONS FOR EACH STEP TO HELP ME UNDERSTAND WHAT IS GOING ON, I WILL THUMBS UP.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started