Answered step by step

Verified Expert Solution

Question

1 Approved Answer

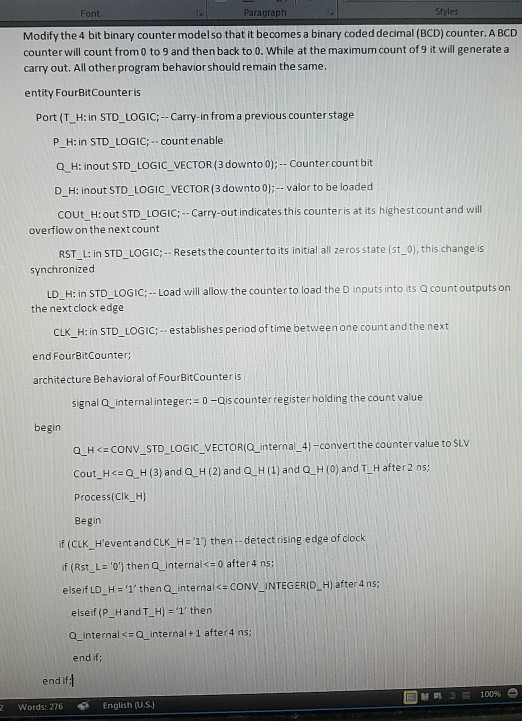

need help with this VHDL problem. Font Paragraph Styles Modify the 4 bit binary counter model so that it becomes a binary coded decimal (BCD)

need help with this VHDL problem.

Font Paragraph Styles Modify the 4 bit binary counter model so that it becomes a binary coded decimal (BCD) counter. A BCD counter will count from 0 to 9 and then back to 0. While at the maximum count of 9 it will generate a carry out. All other program behavior should remain the same. entity FourBitCounteris Port (T_H: in STD_LOGIC;--Carry-in from a previous counter stage PH: in STD LOGIC;.. count enable Q H: inout STD_LOGIC_VECTOR (3 downto o);- - Counter count bit D-H: inout STD-LOGIC VECTO R (3 downto 0);valor to be loaded cout-H: out STD-LOGIC;-Carry-out indicates this counter is at its highest count and will - overflow on the nextcount RST L: in STD_LOGIC;--Resets the counterto its initial all zeros state (st_0), this change is synchronized LD_ H: in STD LOGIC;-Load will allow the counterto load the D inputs into its a count outputs on the next clock edge CLK_H:in STD_LOGIC; establishes period of time between one count and the next end FourBitCounter architecture Behavioral of FourBitCounteris signal Q _internalinteger: 0-ais counter register holding the count value begin QH CONV-STD-LOGIC-VECTOR(Q-internal-41-convert the countervalue to SLV Cout-HStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started