Question

Need to implement a 32-bit adder, shifter and ALU in Verilog code. Test files provided at the end ______________________________________________________________ Project.v //32-bit adder //To get all

Need to implement a 32-bit adder, shifter and ALU in Verilog code. Test files provided at the end

______________________________________________________________

Project.v

//32-bit adder

//To get all scores, you cannot use arithmetic operators in this module.

module adder(input [31:0] x,

input [31:0] y,

input ci,

output reg co,

output reg [31:0] s);

//write your code here

endmodule

//32-bit shifter

//To get all scores, you cannot use shift operators in this module.

module shifter(input [31:0] x,

input [4:0] c,

input [1:0] op,

output reg [31:0] y);

//write your code here

endmodule

//32-bit ALU

//To get all scores, you cannot use arithmetic operators in this module.

module ALU(

input [31:0] a,

input [31:0] b,

input [2:0] op,

output reg [31:0] s);

//write your code here

endmodule

________________________

Adder.v (test file)

module add_tb;

reg [31:0] x_tb;

reg [31:0] y_tb;

reg ci_tb;

wire co_tb;

wire [31:0] s_tb;

adder a(x_tb, y_tb, ci_tb, co_tb, s_tb);

initial begin

$monitor("summand1 is %d, summand2 is %d, ci is %d, co is %d, s is %d", x_tb, y_tb, ci_tb, co_tb, s_tb);

//$monitor("Ouput s is %d", s_tb);

$dumpfile("add.vcd");

$dumpvars(0, a);

x_tb = 2;

y_tb = 4;

ci_tb = 0;

#10

x_tb = 3;

#10

x_tb = 4;

y_tb = 23;

#10

x_tb = 23;

y_tb = 27;

ci_tb = 1;

#10

ci_tb = 0;

x_tb = ~0;

y_tb = 1;

#10

ci_tb = 1;

end

endmodule

________________________

Shifter.v (test file)

module Shift_tb;

reg[31:0] in_tb;

reg[4:0] c_tb;

reg[1:0] op_tb;

wire[31:0] y_tb;

shifter s(in_tb, c_tb, op_tb, y_tb);

initial begin

$monitor("input is %h, shift is %d, operation is %b, y is %h", in_tb, c_tb, op_tb, y_tb);

$dumpfile("Shift.vcd");

$dumpvars(0, s);

in_tb = 'h80000001;

c_tb = 4;

op_tb = 0;

#10

op_tb = 1;

#10

op_tb = 2;

#10

op_tb = 3;

end

endmodule

________________________

ALU.v (test file) module ALU_tb;

reg [31:0] a_tb;

reg [31:0] b_tb;

reg [2:0] op_tb;

wire [31:0] s_tb;

ALU al(a_tb, b_tb, op_tb, s_tb);

initial begin

$monitor("a is %d, b is %d, op is %d, s is %h", a_tb, b_tb, op_tb, s_tb);

$dumpfile("ALU.vcd");

$dumpvars(0, al);

a_tb = 1;

b_tb = -1;

op_tb = 0;

#10

op_tb = 1;

#10

op_tb = 2;

#10

op_tb = 3;

#10

op_tb = 4;

#10

op_tb = 5;

#10

op_tb = 6;

#10

op_tb = 7;

end

endmodule

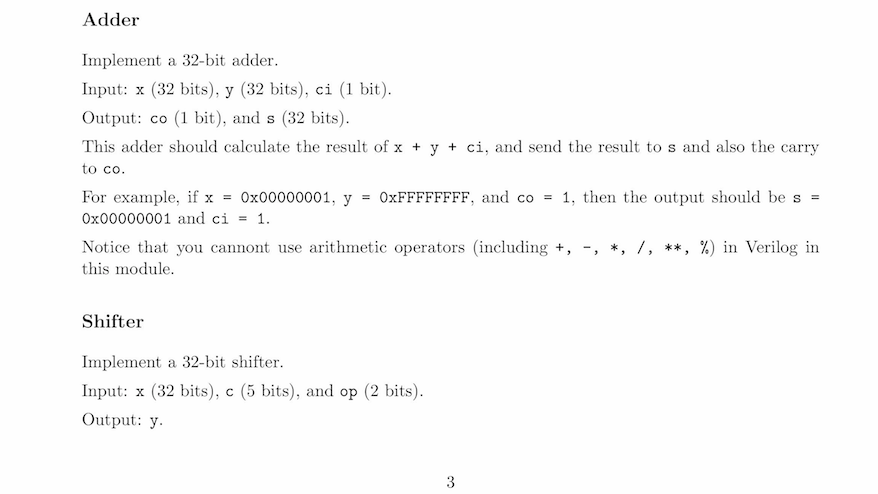

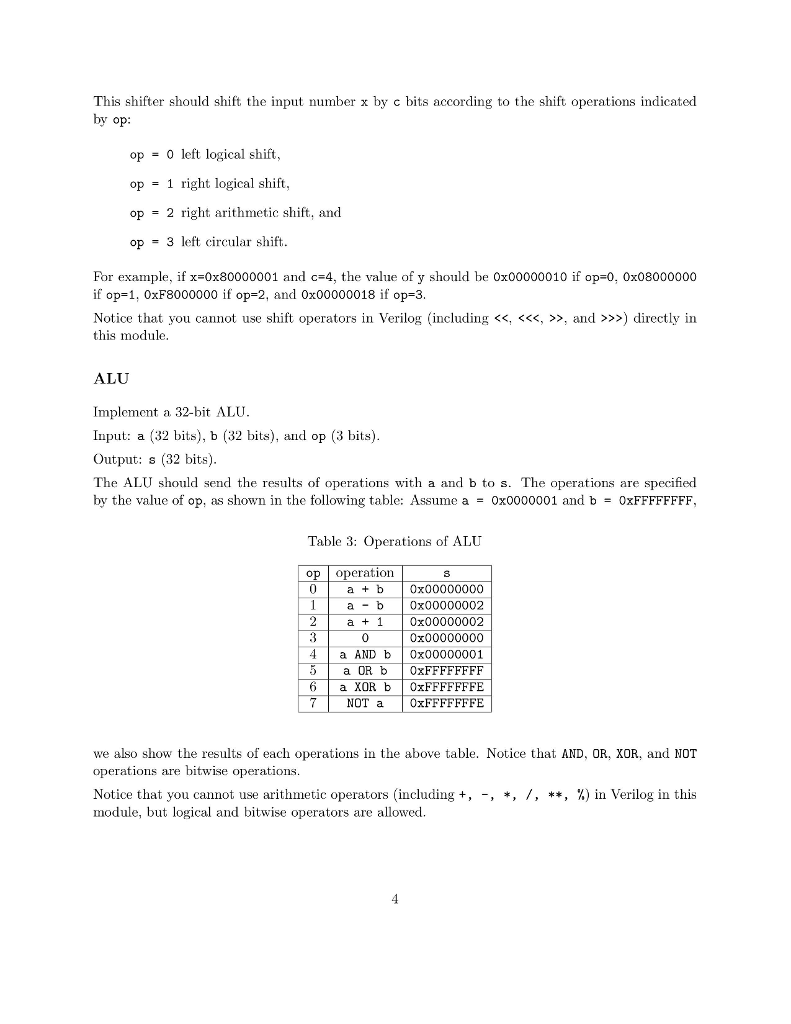

Adder nt a 32-bit adder. Input: x (32 bits), y (32 bits), ci (1 bit) Output: co (1 bit), and s (32 bits). This adder should calculate the result of x y ci, and send the result to s and also the carry to co. For example, if x = 0:00000001, y = 0xFFFFFFFF, and co = 1, then the output should be s = 0x00000001 and ci 1. Notice that you cannont use arithmetic operators (including +, -, *, /, *+, %) in Verilog in this module Shifter Implement a 32-bit shifter Input: x (32 bits), c (5 bits), and op (2 bits). Output: y. Adder nt a 32-bit adder. Input: x (32 bits), y (32 bits), ci (1 bit) Output: co (1 bit), and s (32 bits). This adder should calculate the result of x y ci, and send the result to s and also the carry to co. For example, if x = 0:00000001, y = 0xFFFFFFFF, and co = 1, then the output should be s = 0x00000001 and ci 1. Notice that you cannont use arithmetic operators (including +, -, *, /, *+, %) in Verilog in this module Shifter Implement a 32-bit shifter Input: x (32 bits), c (5 bits), and op (2 bits). Output: yStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started