Question: needed only C part please in 1 hour 1. (a) Explain why it is important for processor designers to release ISA specifications. (10%) (b) Figure

needed only C part please in 1 hour

needed only C part please in 1 hour

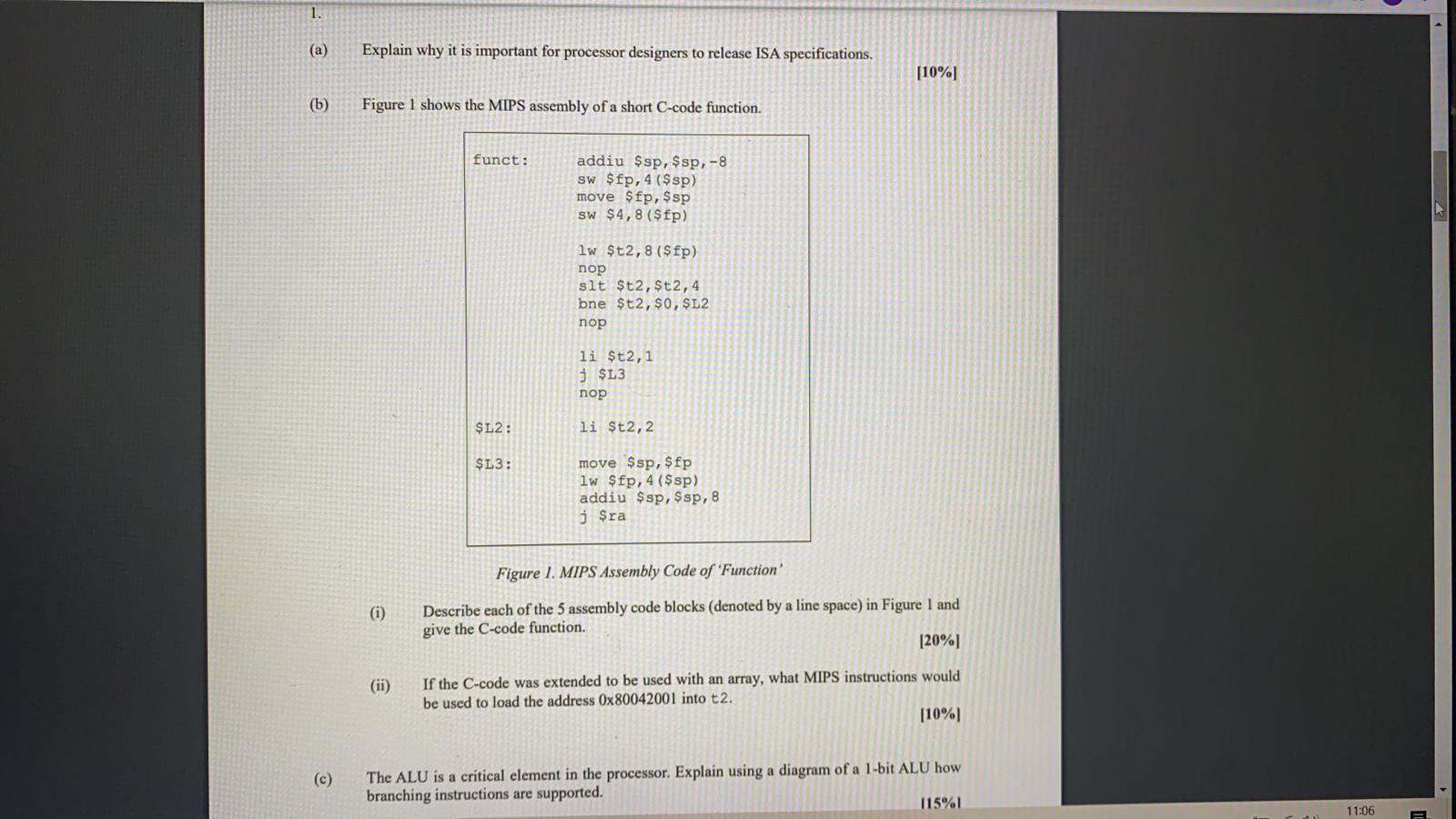

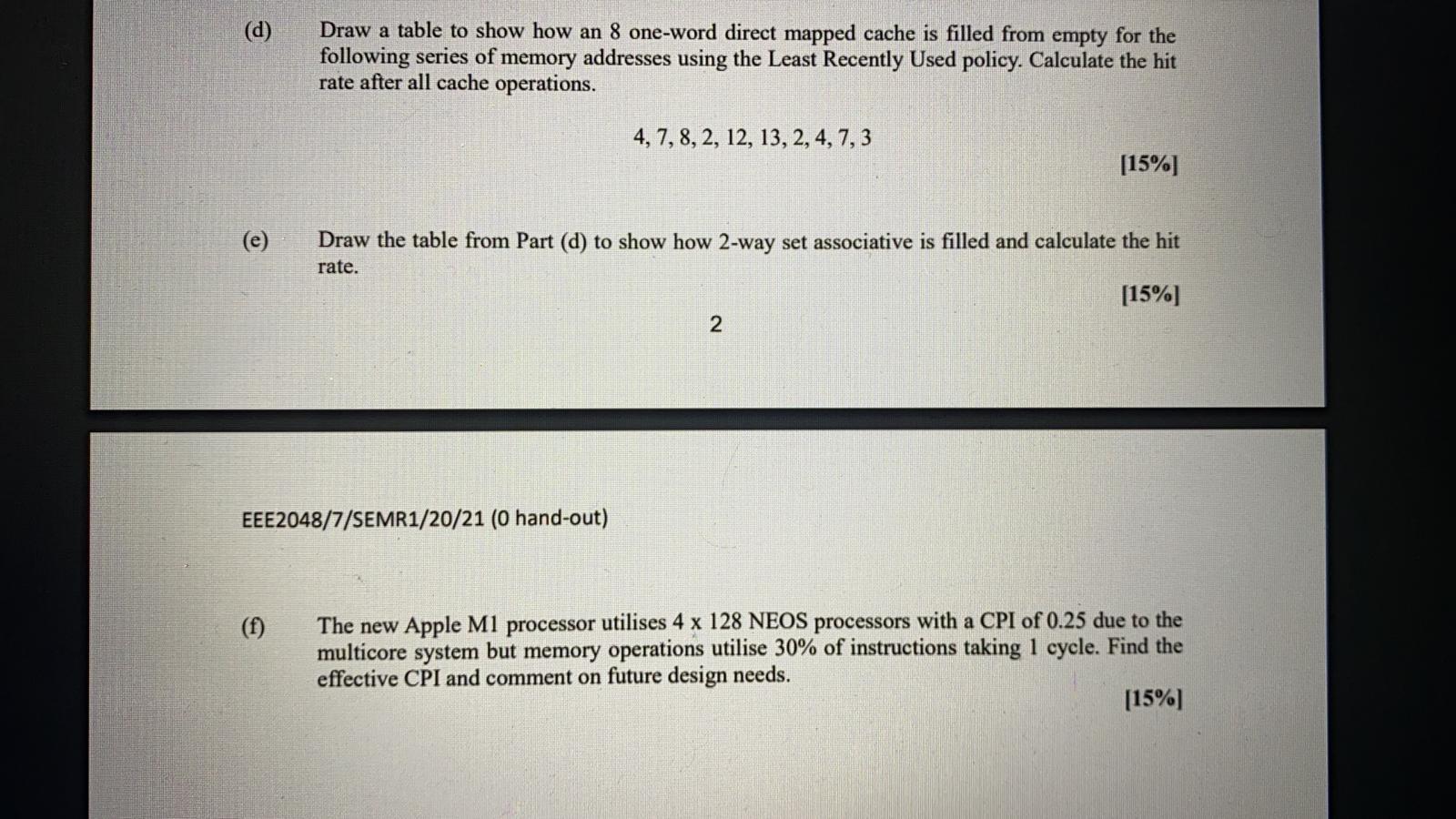

1. (a) Explain why it is important for processor designers to release ISA specifications. (10%) (b) Figure 1 shows the MIPS assembly of a short C-code function. funct: addiu $sp,$sp, -8 sw $fp, 4 (Ssp) move $fp,$sp SW $4,8 ($fp) lw $t2,8($fp) nop slt $t2, St2,4 bne $t2, 90, $L2 nop li $t2,1 j $L3 nop SL2: li $t2,2 $13: move $sp,$fp lw $fp, 4($sp) addiu $sp,$sp, 8 j Sra Figure 1. MIPS Assembly Code of 'Function (i) Describe each of the 5 assembly code blocks (denoted by a line space) in Figure 1 and give the C-code function. (20%) (ii) If the C-code was extended to be used with an array, what MIPS instructions would be used to load the address 0x80042001 into t2. [10%) (c) The ALU is a critical element in the processor. Explain using a diagram of a 1-bit ALU how branching instructions are supported. 115% 11:06 (d) Draw a table to show how an 8 one-word direct mapped cache is filled from empty for the following series of memory addresses using the Least Recently Used policy. Calculate the hit rate after all cache operations. 4,7,8, 2, 12, 13, 2, 4, 7,3 [15%) (e) Draw the table from Part (d) to show how 2-way set associative is filled and calculate the hit rate. [15%) 2 EEE2048/7/SEMR1/20/21 (0 hand-out) The new Apple M1 processor utilises 4 x 128 NEOS processors with a CPI of 0.25 due to the multicore system but memory operations utilise 30% of instructions taking 1 cycle. Find the effective CPI and comment on future design needs. [15%) 1. (a) Explain why it is important for processor designers to release ISA specifications. (10%) (b) Figure 1 shows the MIPS assembly of a short C-code function. funct: addiu $sp,$sp, -8 sw $fp, 4 (Ssp) move $fp,$sp SW $4,8 ($fp) lw $t2,8($fp) nop slt $t2, St2,4 bne $t2, 90, $L2 nop li $t2,1 j $L3 nop SL2: li $t2,2 $13: move $sp,$fp lw $fp, 4($sp) addiu $sp,$sp, 8 j Sra Figure 1. MIPS Assembly Code of 'Function (i) Describe each of the 5 assembly code blocks (denoted by a line space) in Figure 1 and give the C-code function. (20%) (ii) If the C-code was extended to be used with an array, what MIPS instructions would be used to load the address 0x80042001 into t2. [10%) (c) The ALU is a critical element in the processor. Explain using a diagram of a 1-bit ALU how branching instructions are supported. 115% 11:06 (d) Draw a table to show how an 8 one-word direct mapped cache is filled from empty for the following series of memory addresses using the Least Recently Used policy. Calculate the hit rate after all cache operations. 4,7,8, 2, 12, 13, 2, 4, 7,3 [15%) (e) Draw the table from Part (d) to show how 2-way set associative is filled and calculate the hit rate. [15%) 2 EEE2048/7/SEMR1/20/21 (0 hand-out) The new Apple M1 processor utilises 4 x 128 NEOS processors with a CPI of 0.25 due to the multicore system but memory operations utilise 30% of instructions taking 1 cycle. Find the effective CPI and comment on future design needs. [15%)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts