Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Old MathJax webview make a design as required.. what kind of information is missing? In this experiment, students have to modify the design of their

Old MathJax webview

make a design as required.. what kind of information is missing?

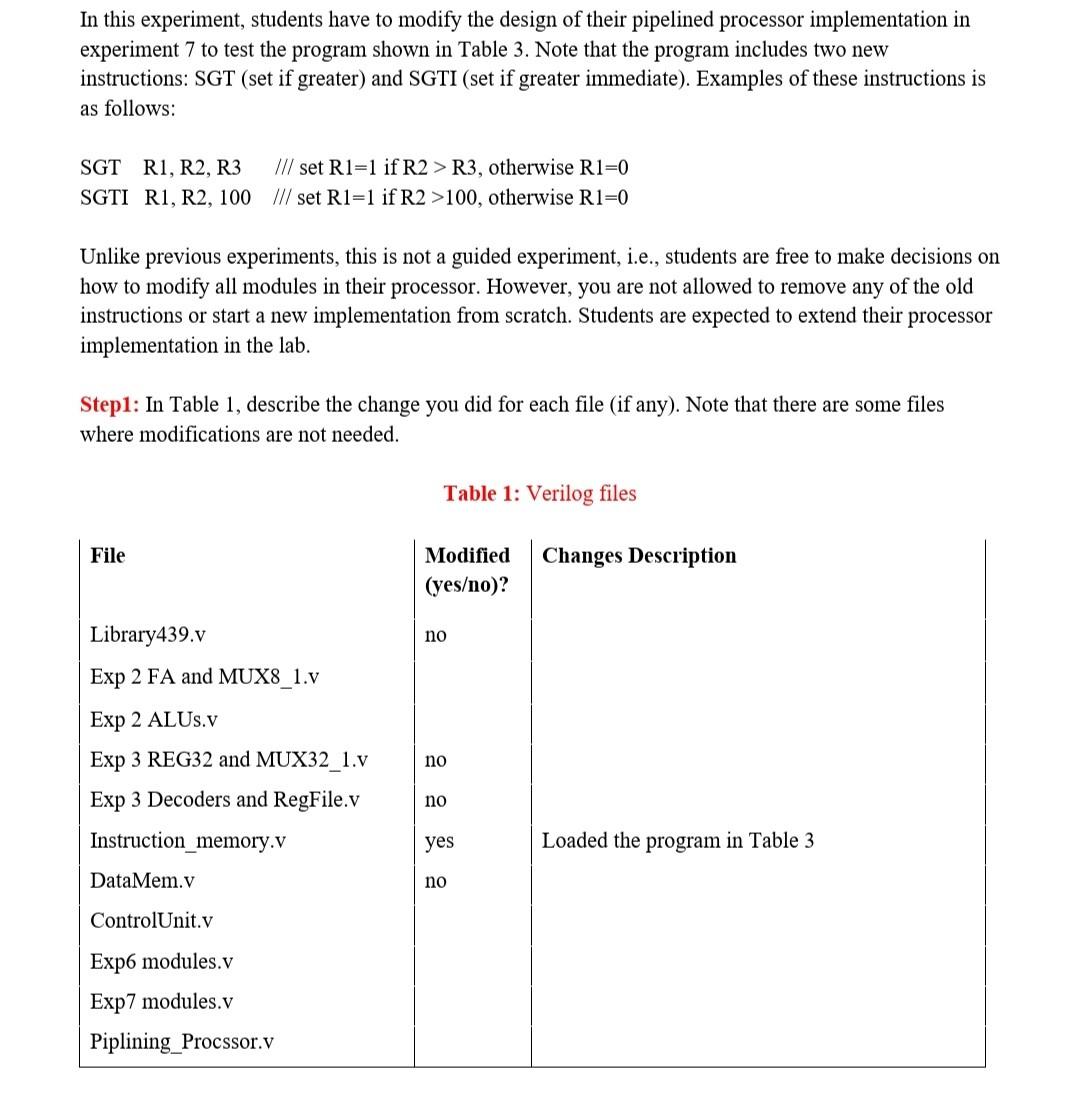

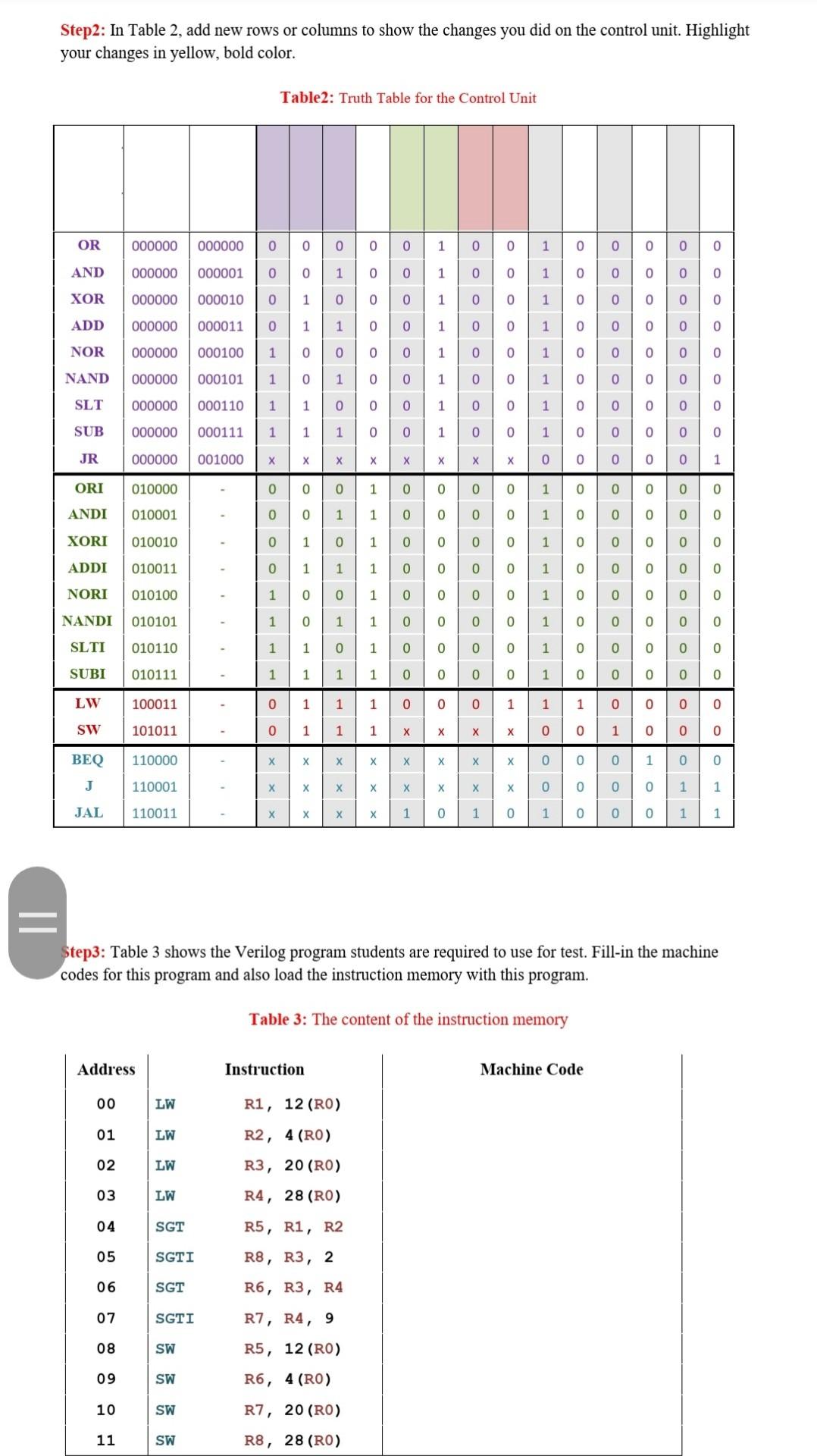

In this experiment, students have to modify the design of their pipelined processor implementation in experiment 7 to test the program shown in Table 3. Note that the program includes two new instructions: SGT (set if greater) and SGTI (set if greater immediate). Examples of these instructions is as follows: SGT R1, R2, R3 /// set Ri=1 if R2 > R3, otherwise R1=0 SGTI R1, R2, 100 /// set Ri=1 if R2 >100, otherwise Ri=0 Unlike previous experiments, this is not a guided experiment, i.e., students are free to make decisions on how to modify all modules in their processor. However, you are not allowed to remove any of the old instructions or start a new implementation from scratch. Students are expected to extend their processor implementation in the lab. Step1: In Table 1, describe the change you did for each file (if any). Note that there are some files where modifications are not needed. Table 1: Verilog files File Changes Description Modified (yeso)? no Library439.v Exp 2 FA and MUX8_1.v Exp 2 ALUS. Exp 3 REG32 and MUX32_1.v no Exp 3 Decoders and RegFile.v no Instruction_memory.v yes Loaded the program in Table 3 DataMem.v no ControlUnit.v Exp6 modules. Exp7 modules. Piplining_Procssor.v Step 2: In Table 2, add new rows or columns to show the changes you did on the control unit. Highlight your changes in yellow, bold color. Table2: Truth Table for the Control Unit OR 000000 000000 0 o|o 0 0 1 0 1 1 0 0 0 0 0 AND 000000 000001 0 1 0 0 1 0 0 1 1 o 0 0 0 XOR 000000 000010 O O O 1 0 0 0 1 0 1 0 0 0 ADD O O O O O O 000000 000011 1 1 0 0 1 0 1 0 0 0 0 O O O O O O NOR 000000 000100 0 0 0 0 0 1 0 1 0 O O O O O O O O NAND o o o o 000000 000101 0 1 0 0 1 o o o o o 1 0 SLT 000000 000110 1 1 0 0 1 0 1 0 SUB 000000 000111 1 1 1 0 0 1 0 0 1 0 0 JR 000000 001000 X X X 0 1 OX ORI 010000 o o o o o o o o o o o o o o o o 1 0 0 0 xoo 1 00 000 0 0 0 0 0 0 o 0 . O O 0 ANDI 010001 1 0 1 0 XORI 010010 1 0 1 0 0 1 0 ADDI 010011 1 1 1 0 0 0 O O O O O O O 0 1 0 NORI o o o o o o 010100 0 0 1 0 0 0 1 0 0 0 O O O O O O o o o o o o o o o o o O O O O O O O NANDI 010101 0 * * * O O O O O O X 1 1 0 0 1 0 SLTI 010110 1 0 1 0 1 0 SUBI 010111 1 1 1 0 0 0 0 1 0 0 LW 100011 1 1 1 0 0 1 0 0 0 0 x 0 SW 101011 1 1 1 X X 1 0 0 0 BEQ 110000 X X X X X 0 1 1 1 00 0 0 0 0 10 0 0 x x x x J 110001 X X X X X O X 0 0 1 1 JAL 110011 X X 1 1 0 0 0 1 1 = Step3: Table 3 shows the Verilog program students are required to use for test. Fill-in the machine codes for this program and also load the instruction memory with this program. Table 3: The content of the instruction memory Address Instruction Machine Code 00 LW R1, 12 (RO) 01 LW R2, 4 (RO) 02 LW R3, 20 (RO) 03 LW R4, 28 (RO) 04 SGT R5, R1, R2 05 SGTI R8, R3, 2 R6, R3, R4 06 SGT 07 SGTI R7, R4, 9 08 SW R5, 12 (RO) 09 SW R6, 4 (RO) 10 SW R7, 20 (RO) 11 SW R8, 28 (RO) Step4: Generate the timing diagram for the program in Table 3, with the below signals (in-order). Note that the test module is already given to you. Clock, reset, enable PC (the output of the program counter) . Instruction (the output of the instruction memory) The output of the registers R5, R6, R7, and R8 The readdata, writedata, address, memwrite, and memread signals for the data memory Paste a screenshot of your timing diagram below. Make sure it is clear and readable. Step5: To make it easier for us to grade your work, in below, copy/paste all modified or new modules in your code. Also, highlight in bold font, the modified lines in the module. For example, if you made changes on the processor module, then copy/paste the entire processor module and highlight only the lines that have been modified. It is okay to use several pages for this step. However, please try your best to show your code in an easy-to-read fashion and avoid large fontsStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started