Answered step by step

Verified Expert Solution

Question

1 Approved Answer

On the vertical axis is the number of cycles for one memory read instruction. The horizontal axis is the size of the test array in

On the vertical axis is the number of cycles for one memory read instruction. The horizontal axis is the size

of the test array in bytes.

How many levels of caching is used by computer A and how large are these caches?

How many levels of caching is used by computer and how large are these caches?B Now consider the following two implementations of a horizontal flip and copy of the matrix. Again

assume that the src matrix starts at address and that the dest matrix follows immediately follows it

void copynflipmatrixint destROWSCOLS int srcROWSCOLS

int i j;

for ROWS;

for COLS ;

dest;

What is the cache miss rate if ROWS and COLS

Miss rate

What is the cache miss rate if ROWS and COLS

Miss rate

void copynflipmatrixint destROWSCOLS int srcROWSCOLS

int i j;

for COLS ;

for ROWS;

dest;

What is the cache miss rate if ROWS and COLS

Miss rate

What is the cache miss rate if ROWS and COLS

Miss rate Problem points:

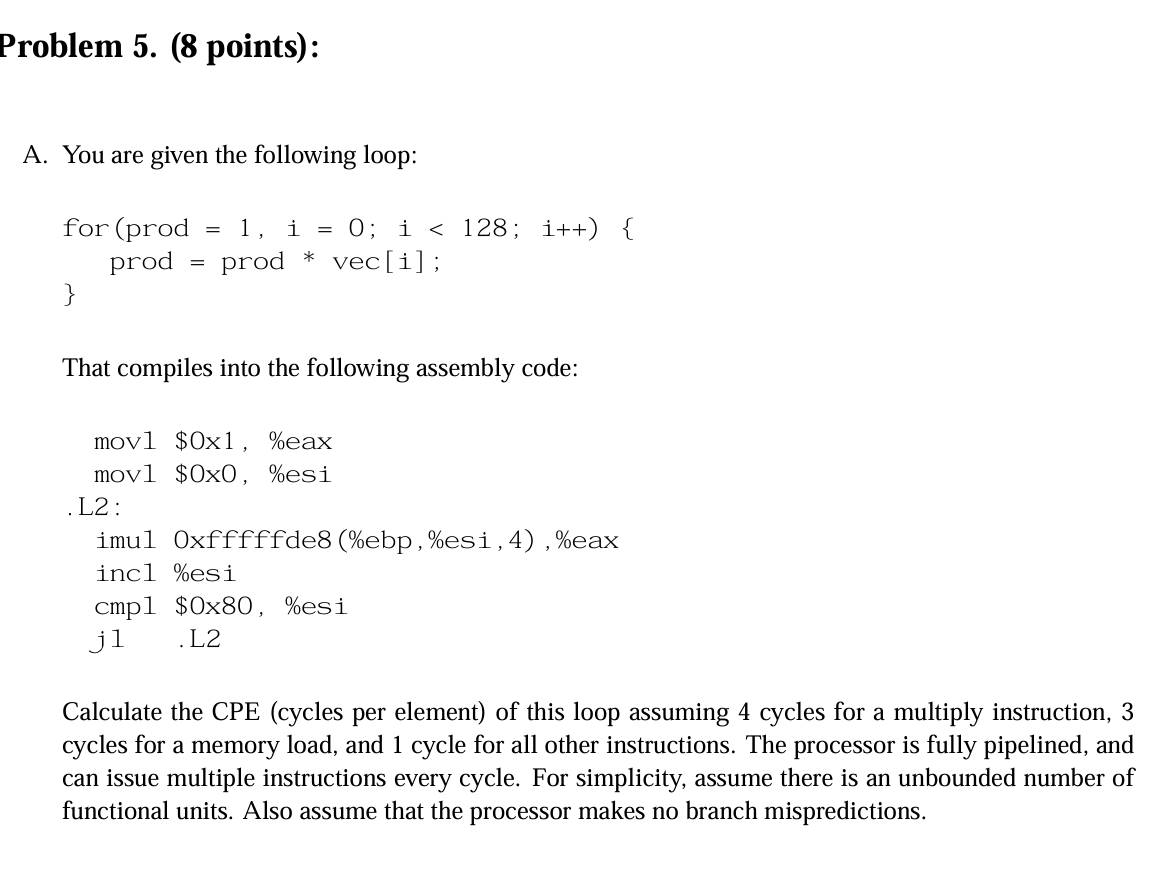

A You are given the following loop:

for

prodprod;

That compiles into the following assembly code:

mov $xeax

mov $xesi

L :

imul Oxfffffdeebp, esi, eax

incesi

cmp $xesi

j L

Calculate the CPE cycles per element of this loop assuming cycles for a multiply instruction,

cycles for a memory load, and cycle for all other instructions. The processor is fully pipelined, and

can issue multiple instructions every cycle. For simplicity, assume there is an unbounded number of

functional units. Also assume that the processor makes no branch mispredictions.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started