Question

ONLY USING VHDL PLEASE DO NOT USE VERILOG : In the block diagram given below inputs are fed into the first row of ALU blocks

ONLY USING VHDL PLEASE DO NOT USE VERILOG :

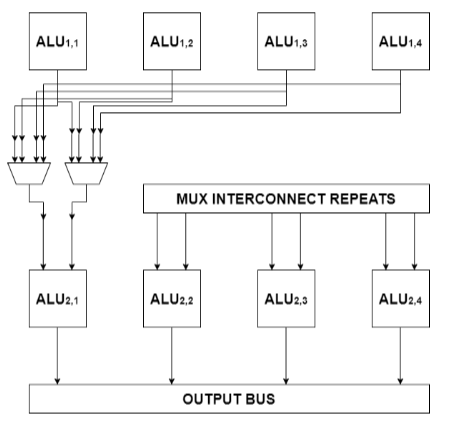

In the block diagram given below inputs are fed into the first row of ALU blocks as shown. Each of the

inputs to the ALUs are 8-bit wide. Program / Configure the ALUs in such a way that the

ALU(1,1) performs a NAND, ALU(1,2) performs a NOR, ALU(1,3) performs an AND,

and ALU(1,4) performs an OR. Program the ALUs in the second row with the following

operations: ALU(2,1) performs an Addition, ALU(2,2) performs a Logical Right Shift,

ALU(2,3) performs an Arithmetic Right Shift, and ALU(2,4) performs a Subtraction. For

this question, use the MUX based interconnect as shown in the block diagram. The codes must be properly commented. (5 + 5 + 5 + 5).

PLEASE INCLUDE VHDL CODE AND ALSO THE TEST BENCH CODE.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started