Question

.org 0 la r31,LOOP la r29,TOP la r1,0 TOP: la r30,-1 shl r30,r30,21 LOOP: st r1,0(r30) addi r30,r30,4 brnz r31,r30 addi r1,r1,1 br r29 stop

.org 0 la r31,LOOP la r29,TOP la r1,0 TOP: la r30,-1 shl r30,r30,21 LOOP: st r1,0(r30) addi r30,r30,4 brnz r31,r30 addi r1,r1,1 br r29 stop .org 4096 ; MYD: .dw 1024 .org 4292870144 MYVGA: .dw 524288

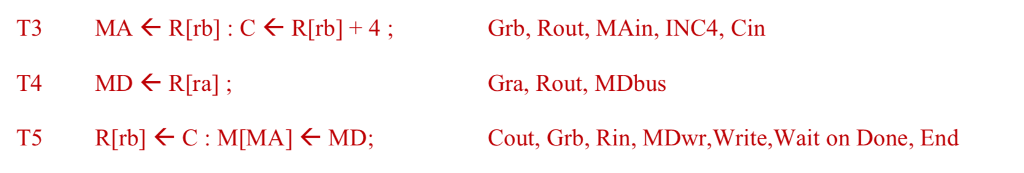

When we look at the assembly code above and think about it for a minute, we see a tight inner loop that writes a single value to the entire framebuffer: LOOP: st r1,0(r30) addi r30,r30,4 brnz r31,r30 The address register, R[30], is incremented until it is incremented to zero, wrapping around to the beginning of memory where the executing program is stored. Careful inspection of the code, however, reveals that address 0 is never written by code. This is an excellent opportunity for us to implement a CISC-type instruction, one we will call Bit Blit, or BLT, that can be used to replace tight loops like this. The new syntax, in this circumstance, will be: LOOP: blt r1,r30 Here, once execution begins, the micro-coded instruction implementation will keep incrementing the base register, R[30], until it reaches zero (0). The general syntax for BLT will be: blt ra,rc Assuming the OP Code for BLT is 00111_2, write the RTN and Control sequence for this new instruction

Its based on. RISC processor

NOTE: He wants something like this :

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started