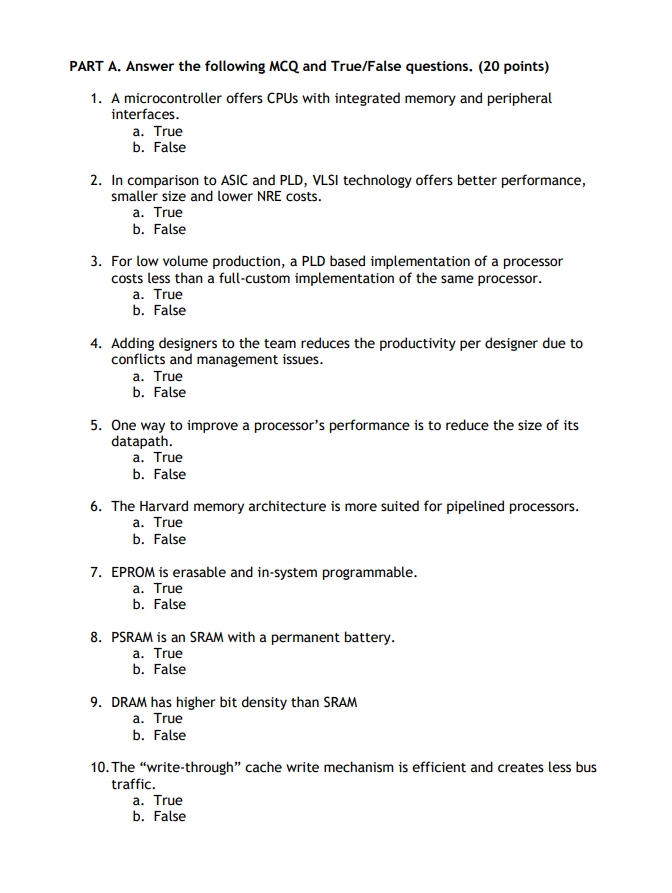

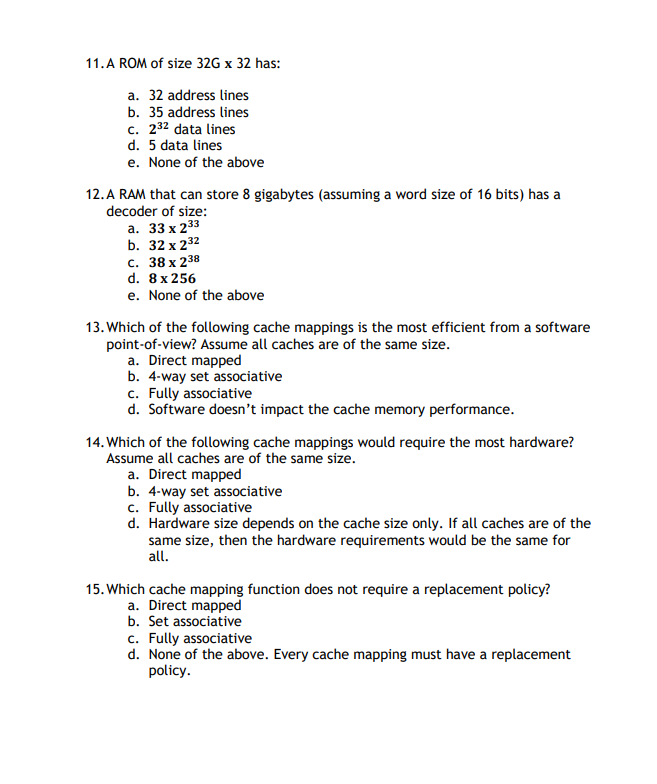

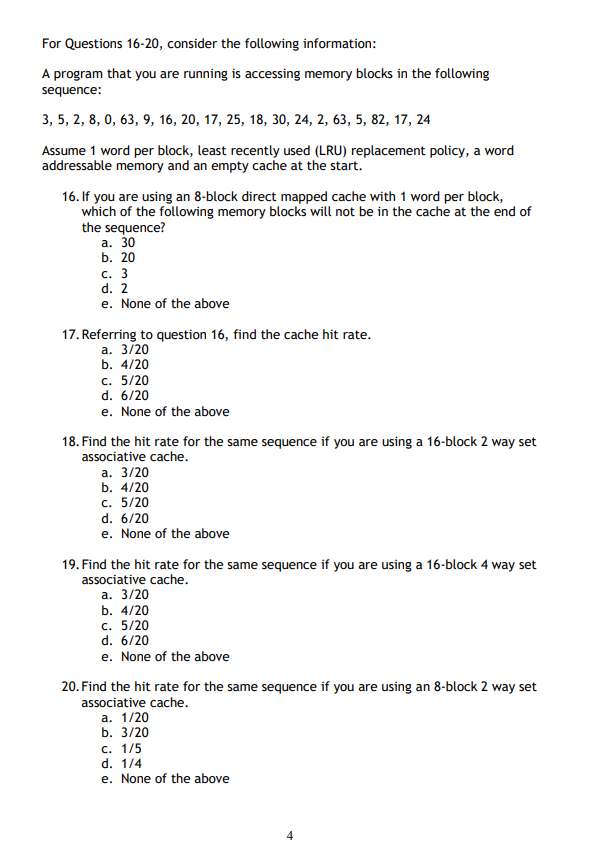

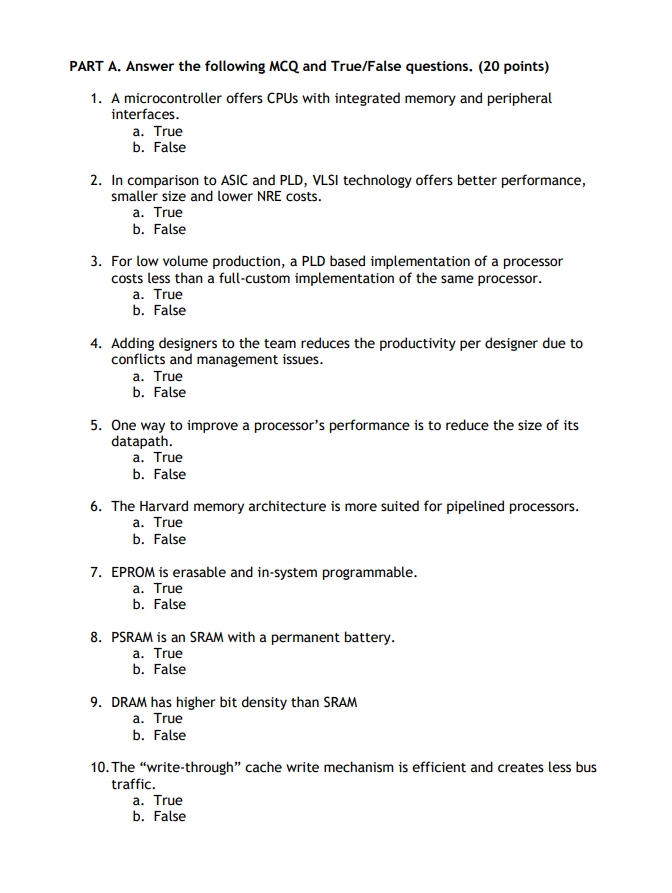

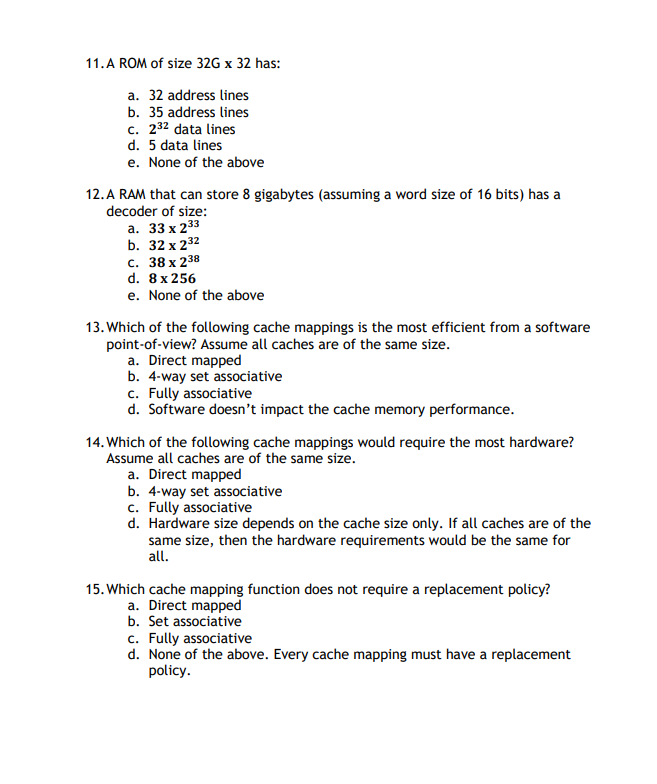

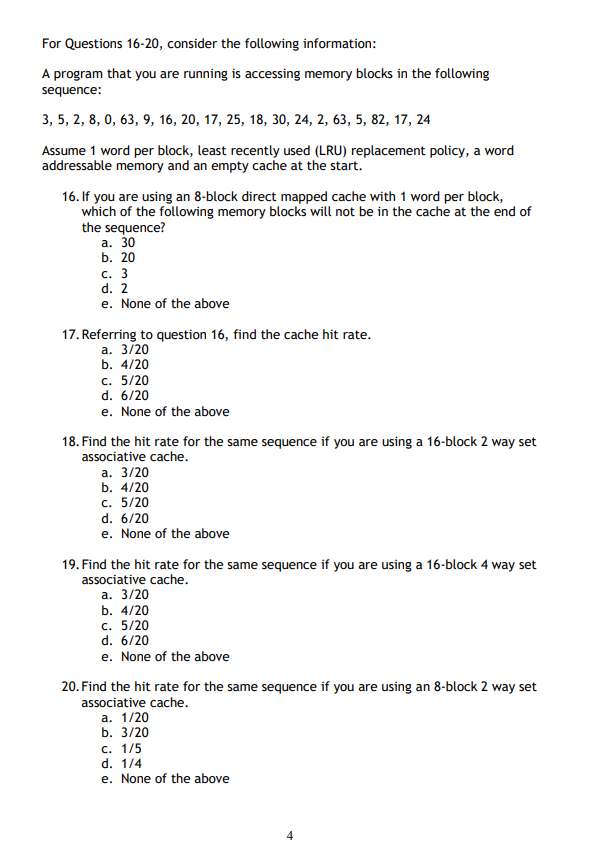

PART A. Answer the following MCQ and True/False questions. (20 points) 1. A microcontroller offers CPUs with integrated memory and peripheral interfaces. a. True b. False 2. In comparison to ASIC and PLD, VLSI technology offers better performance, smaller size and lower NRE costs. a. True b. False 3. For low volume production, a PLD based implementation of a processor costs less than a full-custom implementation of the same processor. a. True b. False 4. Adding designers to the team reduces the productivity per designer due to conflicts and management issues. a. True b. False 5. One way to improve a processor's performance is to reduce the size of its datapath. a. True b. False 6. The Harvard memory architecture is more suited for pipelined processors. a. True b. False 7. EPROM is erasable and in-system programmable. a. True b. False 8. PSRAM is an SRAM with a permanent battery. a. True b. False 9. DRAM has higher bit density than SRAM a. True b. False 10. The write-through cache write mechanism is efficient and creates less bus traffic. a. True b. False 11. A ROM of size 326 x 32 has: a. 32 address lines b. 35 address lines c. 232 data lines d. 5 data lines e. None of the above 12.A RAM that can store 8 gigabytes (assuming a word size of 16 bits) has a decoder of size: a. 33 x 233 b. 32 x 232 c. 38 x 238 d. 8 x 256 e. None of the above 13. Which of the following cache mappings is the most efficient from a software point-of-view? Assume all caches are of the same size. a. Direct mapped b. 4-way set associative C. Fully associative d. Software doesn't impact the cache memory performance. 14. Which of the following cache mappings would require the most hardware? Assume all caches are of the same size. a. Direct mapped b. 4-way set associative c. Fully associative d. Hardware size depends on the cache size only. If all caches are of the same size, then the hardware requirements would be the same for all. 15. Which cache mapping function does not require a replacement policy? a. Direct mapped b. Set associative C. Fully associative d. None of the above. Every cache mapping must have a replacement policy. For Questions 16-20, consider the following information: A program that you are running is accessing memory blocks in the following sequence: 3, 5, 2, 8, 0, 63, 9, 16, 20, 17, 25, 18, 30, 24, 2, 63, 5, 82, 17, 24 Assume 1 word per block, least recently used (LRU) replacement policy, a word addressable memory and an empty cache at the start. 16. If you are using an 8-block direct mapped cache with 1 word per block, which of the following memory blocks will not be in the cache at the end of the sequence? a. 30 b. 20 C. 3 d. 2 e. None of the above 17. Referring to question 16, find the cache hit rate. a. 3720 b. 4/20 c. 5/20 d. 6/20 e. None of the above 18. Find the hit rate for the same sequence if you are using a 16-block 2 way set associative cache. a. 3/20 b. 4/20 C. 5/20 d. 6/20 e. None of the above 19. Find the hit rate for the same sequence if you are using a 16-block 4 way set associative cache. a. 3/20 b. 4/20 c. 5/20 d. 6/20 e. None of the above 20. Find the hit rate for the same sequence if you are using an 8-block 2 way set associative cache. a. 1/20 b. 3/20 c. 1/5 d. 1/4 e. None of the above 4