Answered step by step

Verified Expert Solution

Question

1 Approved Answer

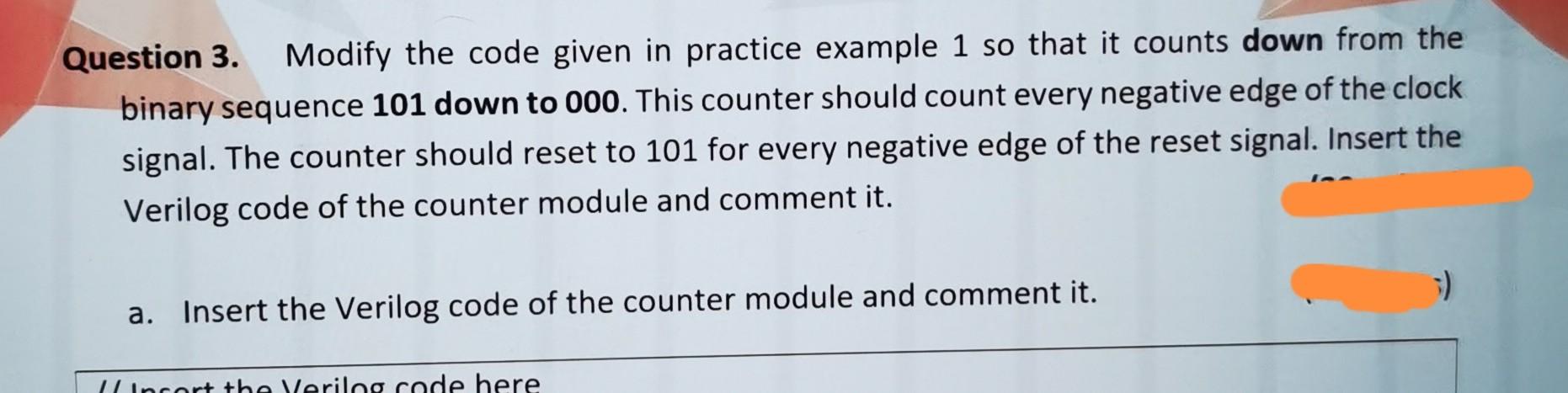

Please a screenshot of the adjusted code. Thank you. Question 3. Modify the code given in practice example 1 so that it counts down from

Please a screenshot of the adjusted code. Thank you.

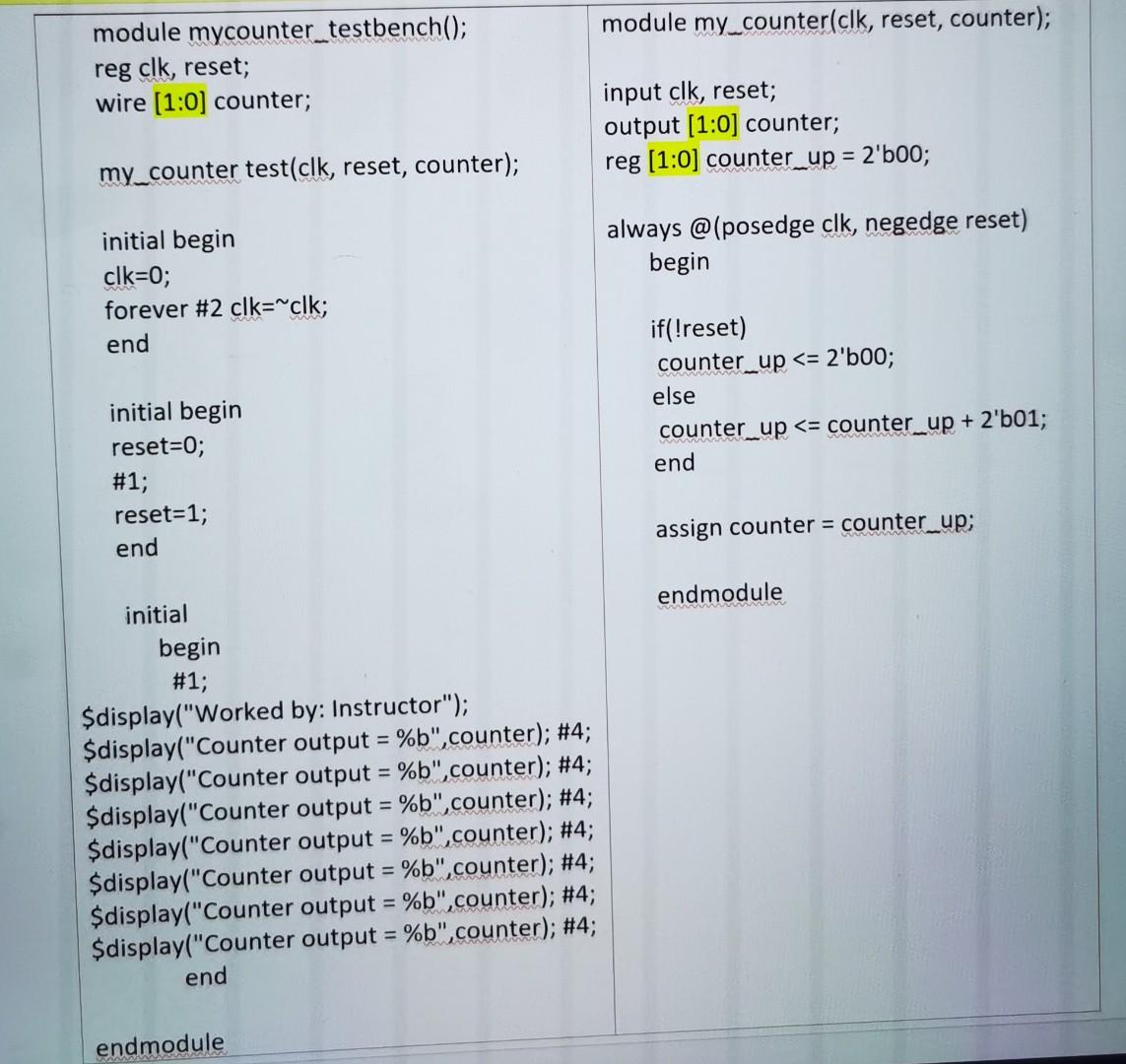

Question 3. Modify the code given in practice example 1 so that it counts down from the binary sequence 101 down to 000. This counter should count every negative edge of the clock signal. The counter should reset to 101 for every negative edge of the reset signal. Insert the Verilog code of the counter module and comment it. 3) a. Insert the Verilog code of the counter module and comment it. Incort the Yerilog code here module my counter(clk, reset, counter); module mycounter_testbench(); reg clk, reset; wire (1:0) counter; input clk, reset; output (1:0) counter; reg (1:0) counter_up = 2'600; - my counter test(clk, reset, counter); always @(posedge clk, negedge reset) begin initial begin clk=0; forever #2 clk=~clk; end if(!reset) counter_upStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started