Answered step by step

Verified Expert Solution

Question

1 Approved Answer

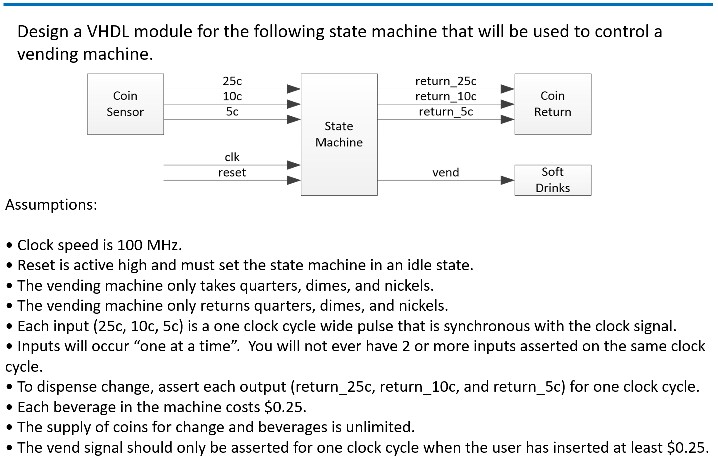

please send the testbench as well. Thank you, Design a VHDL module for the following state machine that will be used to control a vending

please send the testbench as well. Thank you,

Design a VHDL module for the following state machine that will be used to control a vending machine 25c 10c return 25c return 10c return 5c Coin Sensor Return State Machine clk reset vend Soft Drinks Assumptions Clock speed is 100 MHz * Reset is active high and must set the state machine in an idle state . The vending machine only takes quarters, dimes, and nickels . The vending machine only returns quarters, dimes, and nickels . Each input (25c, 1Oc, 5c) is a one clock cycle wide pulse that is synchronous with the clock signal * Inputs will occur "one at a time". You will not ever have 2 or more inputs asserted on the same clock cycle . To dispense change, assert each output (return-25c, return-10c, and return-5c) for one clock cycle . Each beverage in the machine costs $0.25 * The supply of coins for change and beverages is unlimited . The vend signal should only be asserted for one clock cycle when the user has inserted at least $0.25Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started