Answered step by step

Verified Expert Solution

Question

1 Approved Answer

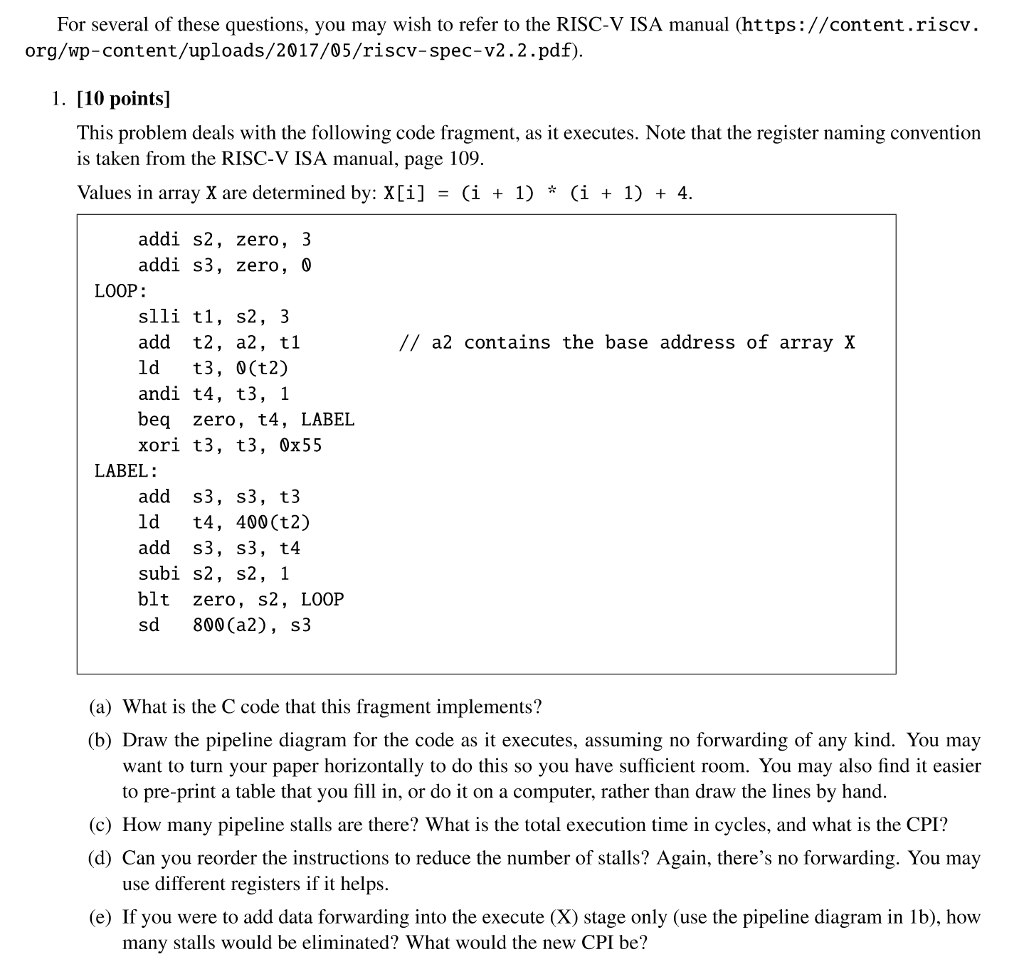

Please show all work, Thanks in advance For several of these questions, you may wish to refer to the RISC-V ISA manual (https://content.riscv. ora/wp-content/uploads/2017/05/riscv-spec-v2.2.pdf) 1.

Please show all work, Thanks in advance

For several of these questions, you may wish to refer to the RISC-V ISA manual (https://content.riscv. ora/wp-content/uploads/2017/05/riscv-spec-v2.2.pdf) 1. [10 points] This problem deals with the following code fragment, as it executes. Note that the register naming convention is taken from the RISC-V ISA manual, page 109 Values in array Xare determined by, x[i] = (1 + 1) * (1 + 1) + 4 addi s2, zero, 3 addi s3, zero, 0 LOOP: slli t1, s2, 3 add t2, a2, t1 ld t3, 0(t2) andi t4, t3, 1 beq zero, t4, LABEL xori t3, t3, Ox55 // a2 contains the base address of array X LABEL: add s3, s3, t3 ld t4, 400 (t2) add s3, s3, t4 subi s2, s2, 1 blt zero, s2, LOOP sd80O (a2), s3 (a) What is the C code that this fragment implements? (b) Draw the pipeline diagram for the code as it executes, assuming no forwarding of any kind. You may want to turn your paper horizontally to do this so you have sufficient room. You may also find it easier to pre-print a table that you fill in, or do it on a computer, rather than draw the lines by hand (c) How many pipeline stalls are there? What is the total execution time in cycles, and what is the CPI? (d) Can you reorder the instructions to reduce the number of stalls? Again, there's no forwarding. You may use different registers if it helps (e) If you were to add data forwarding into the execute (X) stage only (use the pipeline diagram in lb), how many stalls would be eliminated? What would the new CPI be? For several of these questions, you may wish to refer to the RISC-V ISA manual (https://content.riscv. ora/wp-content/uploads/2017/05/riscv-spec-v2.2.pdf) 1. [10 points] This problem deals with the following code fragment, as it executes. Note that the register naming convention is taken from the RISC-V ISA manual, page 109 Values in array Xare determined by, x[i] = (1 + 1) * (1 + 1) + 4 addi s2, zero, 3 addi s3, zero, 0 LOOP: slli t1, s2, 3 add t2, a2, t1 ld t3, 0(t2) andi t4, t3, 1 beq zero, t4, LABEL xori t3, t3, Ox55 // a2 contains the base address of array X LABEL: add s3, s3, t3 ld t4, 400 (t2) add s3, s3, t4 subi s2, s2, 1 blt zero, s2, LOOP sd80O (a2), s3 (a) What is the C code that this fragment implements? (b) Draw the pipeline diagram for the code as it executes, assuming no forwarding of any kind. You may want to turn your paper horizontally to do this so you have sufficient room. You may also find it easier to pre-print a table that you fill in, or do it on a computer, rather than draw the lines by hand (c) How many pipeline stalls are there? What is the total execution time in cycles, and what is the CPI? (d) Can you reorder the instructions to reduce the number of stalls? Again, there's no forwarding. You may use different registers if it helps (e) If you were to add data forwarding into the execute (X) stage only (use the pipeline diagram in lb), how many stalls would be eliminated? What would the new CPI beStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started