Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Pleasee: Based on the solution provided, solve the rest of the questions please ASAP, I need it quicklyyyyyyyyyyyyyyyyyyyyyyyyyyyyyyyy Q4: Consider a direct mapped cache with

Pleasee: Based on the solution provided, solve the rest of the questions please ASAP, I need it quicklyyyyyyyyyyyyyyyyyyyyyyyyyyyyyyyy

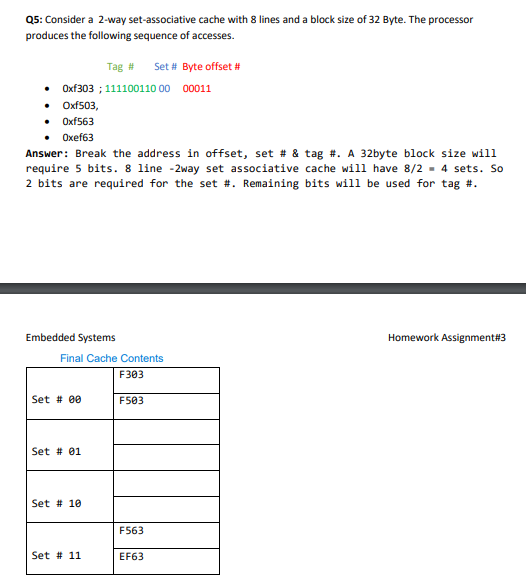

Q4: Consider a direct mapped cache with 8 lines and a block size of 32 Byte. The processor produces the following sequence of accesses - 0x3f1f, 0011111100011111 - Ox3f2f, 0011111100101111 - Ox3f2e, 0011111100101110 - 0x3e1f, 0011111000011111 What are the final contents of the cache. Answer: Break the address in offset, line \# \& tag \#. A 32-byte block size will require 5 bits. 8 -line cache requires 3 bits for the line \#. Remaining bits will be used for tag \#. Note: 03f2f and 3f2e are not in conflict as these addresses are in the same block. Whereas line 000 is first loaded with 3f1f and later replaced with 3e1f. Q5: Consider a 2-way set-associative cache with 8 lines and a block size of 32 Byte. The processor produces the following sequence of accesses. Tag \# Set \# Byte offset \# - 0xf303;1111001100000011 - Oxf503, - 0xf563 - 0xef63 Answer: Break the address in offset, set \# \& tag \#. A 32 byte block size will require 5 bits. 8 line -2 way set associative cache will have 8/2=4 sets. So 2 bits are required for the set \#. Remaining bits will be used for tag \#. Embedded Systems Homework Assignment\#3

Q4: Consider a direct mapped cache with 8 lines and a block size of 32 Byte. The processor produces the following sequence of accesses - 0x3f1f, 0011111100011111 - Ox3f2f, 0011111100101111 - Ox3f2e, 0011111100101110 - 0x3e1f, 0011111000011111 What are the final contents of the cache. Answer: Break the address in offset, line \# \& tag \#. A 32-byte block size will require 5 bits. 8 -line cache requires 3 bits for the line \#. Remaining bits will be used for tag \#. Note: 03f2f and 3f2e are not in conflict as these addresses are in the same block. Whereas line 000 is first loaded with 3f1f and later replaced with 3e1f. Q5: Consider a 2-way set-associative cache with 8 lines and a block size of 32 Byte. The processor produces the following sequence of accesses. Tag \# Set \# Byte offset \# - 0xf303;1111001100000011 - Oxf503, - 0xf563 - 0xef63 Answer: Break the address in offset, set \# \& tag \#. A 32 byte block size will require 5 bits. 8 line -2 way set associative cache will have 8/2=4 sets. So 2 bits are required for the set \#. Remaining bits will be used for tag \#. Embedded Systems Homework Assignment\#3 Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started