Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Post a question Design a sequential circuit that performs division by repeated subtractions. At each clock cycle cct performs subtraction until a stop condition occurs.

Post a question

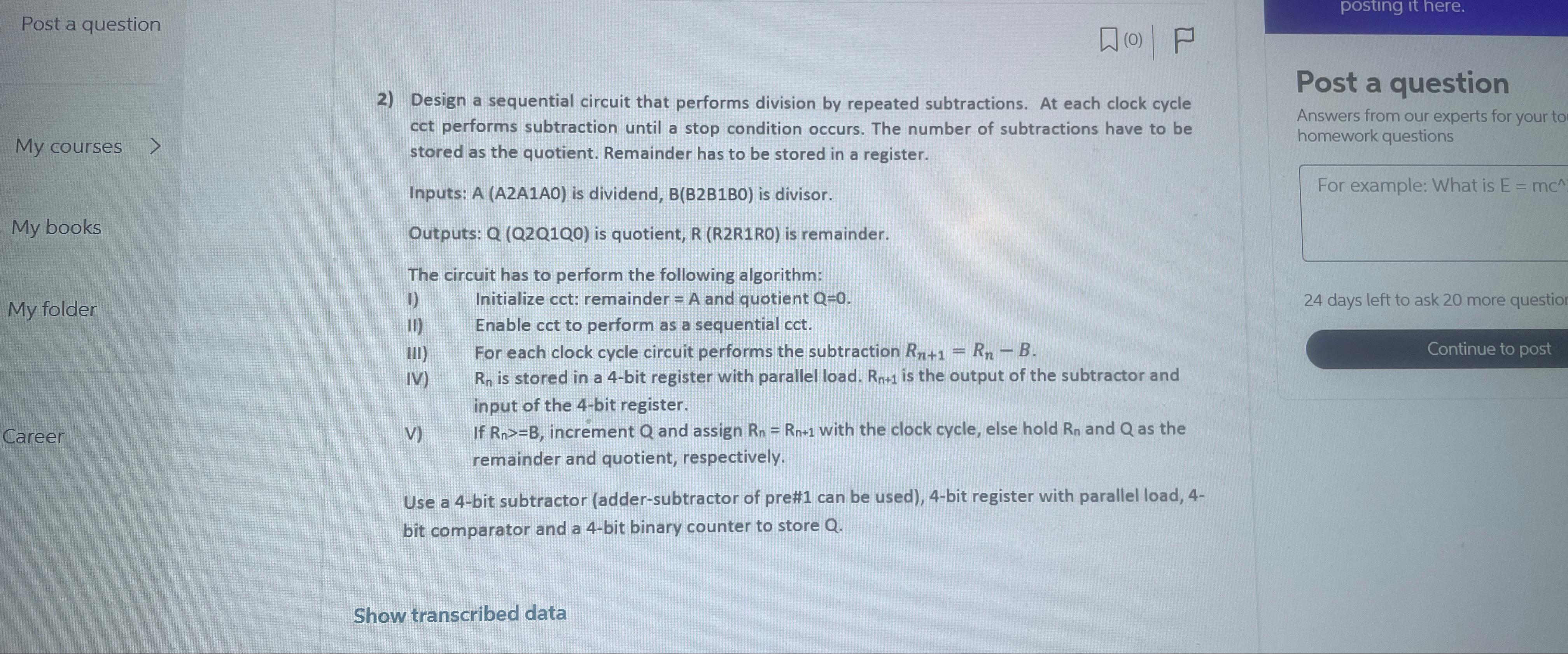

Design a sequential circuit that performs division by repeated subtractions. At each clock cycle cct performs subtraction until a stop condition occurs. The number of subtractions have to be stored as the quotient. Remainder has to be stored in a register.

Inputs: is dividend, is divisor.

Outputs: Q QQQ is quotient, R RRR is remainder.

The circuit has to perform the following algorithm:

I Initialize cct: remainder A and quotient

II Enable cct to perform as a sequential cct

III For each clock cycle circuit performs the subtraction

IV is stored in a bit register with parallel load. is the output of the subtractor and input of the bit register.

V If increment and assign with the clock cycle, else hold and as the remainder and quotient, respectively.

Use a bit subtractor addersubtractor of pre# can be usedbit register with parallel load, bit comparator and a bit binary counter to store Q

Post a question

Answers from our experts for your to homework questions

For example: What is

days left to ask more questio

Continue to post

Career

posting it here.

My courses

My books

My folder

My folder

Career with the clock cycle, else hold and as the remainder and quotient, respectively. PLS GIVE CIRCUIT DIAGRAM OF THIS

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started