Answered step by step

Verified Expert Solution

Question

1 Approved Answer

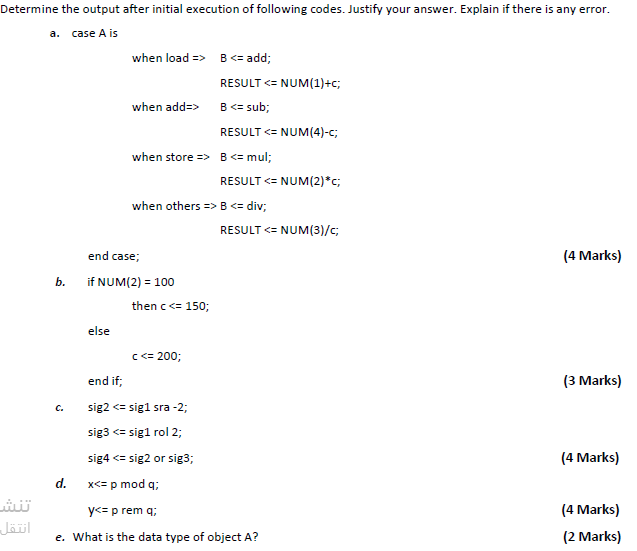

Q1: Consider the below object declarations. signal sig1: std_logic_vector (7 downto 0): =00101001; signal sig2, sig3, sig4: std_logic_vector; constant c: integer: = 75; type OP1

Q1: Consider the below object declarations. signal sig1: std_logic_vector (7 downto 0): =00101001; signal sig2, sig3, sig4: std_logic_vector; constant c: integer: = 75;

type OP1 is (LOAD, STORE, ADD, SUB, MUL, DIV); subtype SUB_OP is OP1 range ADD to DIV; signal A: OP1:=sub; signal B: SUB_OP; Signal P: integer:=11; Signal Q: integer:= 4; Signal X, Y: integer range -10 to 10; type VALUE is array (0 to 4) of integer range 20 to 200; constant NUM: VALUE:=( 25, 50, 100, 150, 200); signal RESULT: integer;

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started