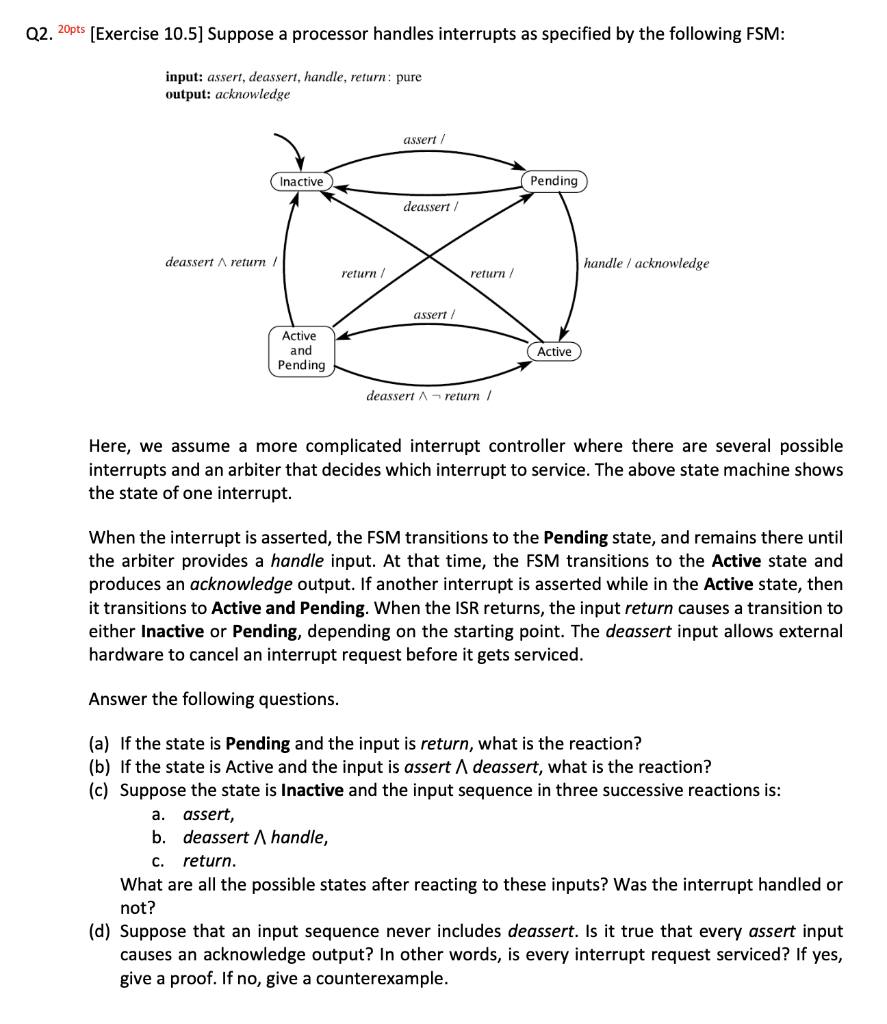

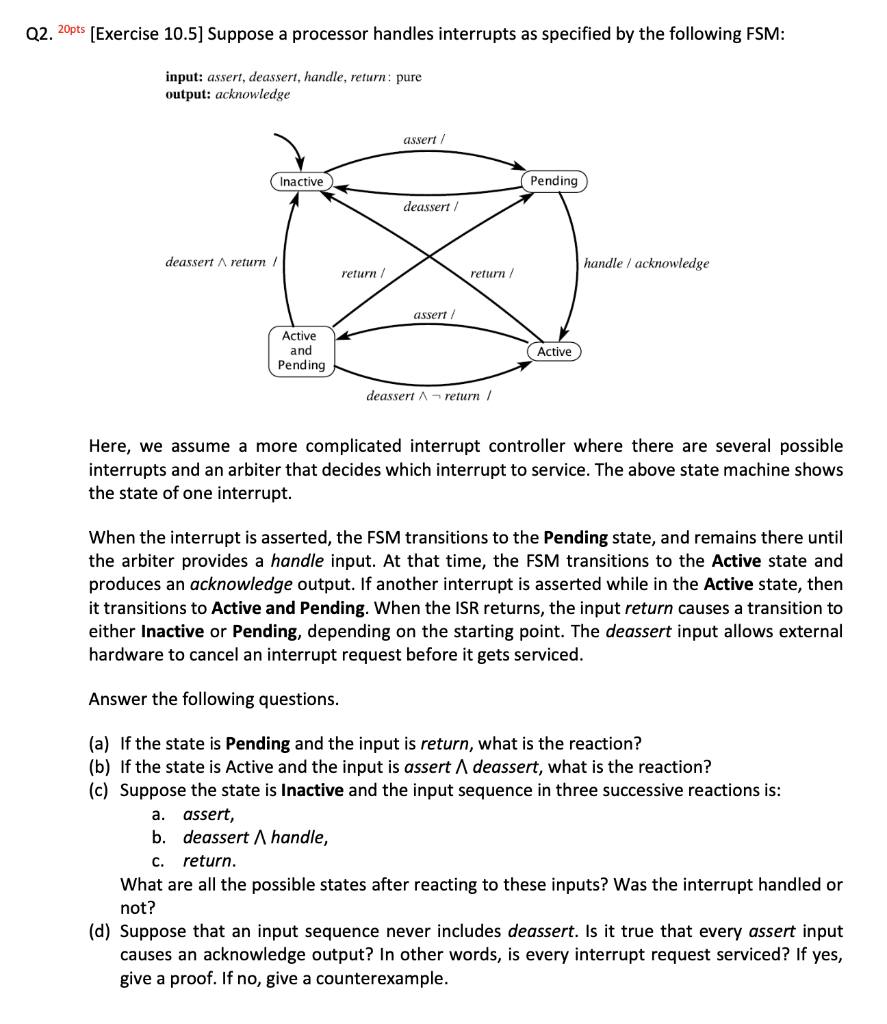

Q2. 20pts (Exercise 10.5] Suppose a processor handles interrupts as specified by the following FSM: input: assert, deassert, handle, return: pure output: acknowledge assert/ Inactive Pending deassert/ deassert return / handle / acknowledge return / return assert/ Active and Pending Active deassert return / Here, we assume a more complicated interrupt controller where there are several possible interrupts and an arbiter that decides which interrupt to service. The above state machine shows the state of one interrupt. When the interrupt is asserted, the FSM transitions to the Pending state, and remains there until the arbiter provides a handle input. At that time, the FSM transitions to the Active state and produces an acknowledge output. If another interrupt is asserted while in the Active state, then it transitions to Active and Pending. When the ISR returns, the input return causes a transition to either Inactive or Pending, depending on the starting point. The deassert input allows external hardware to cancel an interrupt request before it gets serviced. Answer the following questions. a. (a) If the state is Pending and the input is return, what is the reaction? (b) If the state is Active and the input is assert deassert, what is the reaction? (c) Suppose the state is Inactive and the input sequence in three successive reactions is: assert, b. deassert handle, return. What are all the possible states after reacting to these inputs? Was the interrupt handled or not? (d) Suppose that an input sequence never includes deassert. Is it true that every assert input causes an acknowledge output? In other words, is every interrupt request serviced? If yes, give a proof. If no, give a counterexample. C. Q2. 20pts (Exercise 10.5] Suppose a processor handles interrupts as specified by the following FSM: input: assert, deassert, handle, return: pure output: acknowledge assert/ Inactive Pending deassert/ deassert return / handle / acknowledge return / return assert/ Active and Pending Active deassert return / Here, we assume a more complicated interrupt controller where there are several possible interrupts and an arbiter that decides which interrupt to service. The above state machine shows the state of one interrupt. When the interrupt is asserted, the FSM transitions to the Pending state, and remains there until the arbiter provides a handle input. At that time, the FSM transitions to the Active state and produces an acknowledge output. If another interrupt is asserted while in the Active state, then it transitions to Active and Pending. When the ISR returns, the input return causes a transition to either Inactive or Pending, depending on the starting point. The deassert input allows external hardware to cancel an interrupt request before it gets serviced. Answer the following questions. a. (a) If the state is Pending and the input is return, what is the reaction? (b) If the state is Active and the input is assert deassert, what is the reaction? (c) Suppose the state is Inactive and the input sequence in three successive reactions is: assert, b. deassert handle, return. What are all the possible states after reacting to these inputs? Was the interrupt handled or not? (d) Suppose that an input sequence never includes deassert. Is it true that every assert input causes an acknowledge output? In other words, is every interrupt request serviced? If yes, give a proof. If no, give a counterexample. C