Answered step by step

Verified Expert Solution

Question

1 Approved Answer

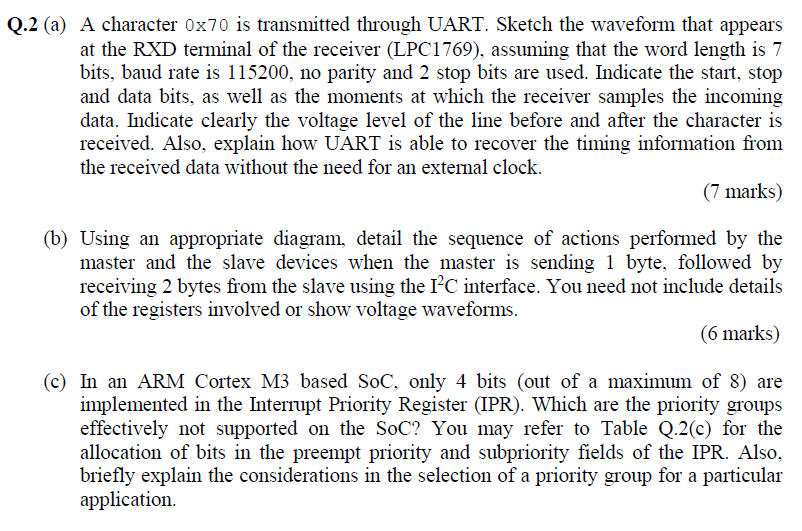

Q.2 (a) A character 0x70 is transmitted through UART. Sketch the waveform that appears at the RXD terminal of the receiver (LPC1769), assuming that

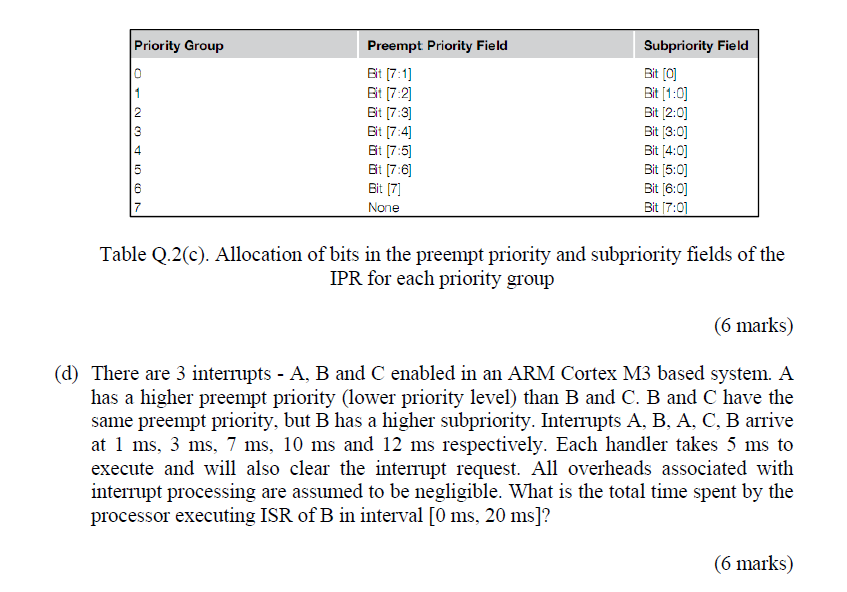

Q.2 (a) A character 0x70 is transmitted through UART. Sketch the waveform that appears at the RXD terminal of the receiver (LPC1769), assuming that the word length is 7 bits, baud rate is 115200, no parity and 2 stop bits are used. Indicate the start, stop and data bits, as well as the moments at which the receiver samples the incoming data. Indicate clearly the voltage level of the line before and after the character is received. Also, explain how UART is able to recover the timing information from the received data without the need for an external clock. (7 marks) (b) Using an appropriate diagram, detail the sequence of actions performed by the master and the slave devices when the master is sending 1 byte, followed by receiving 2 bytes from the slave using the IC interface. You need not include details of the registers involved or show voltage waveforms. (6 marks) (c) In an ARM Cortex M3 based SoC, only 4 bits (out of a maximum of 8) are implemented in the Interrupt Priority Register (IPR). Which are the priority groups effectively not supported on the SoC? You may refer to Table Q.2(c) for the allocation of bits in the preempt priority and subpriority fields of the IPR. Also, briefly explain the considerations in the selection of a priority group for a particular application. Priority Group ON 10 ON 6 7 Preempt Priority Field Bit [7:1] Bit [7:2] Bit [7:3] Bit [7:4] Bit [7:5] Bit [7:6] Bit [7] None Subpriority Field Bit [0] Bit [1:0] Bit [2:0] Bit [3:0] Bit [4:0] Bit [5:0] Bit [6:0] Bit [7:01 Table Q.2(c). Allocation of bits in the preempt priority and subpriority fields of the IPR for each priority group (6 marks) (d) There are 3 interrupts - A, B and C enabled in an ARM Cortex M3 based system. A has a higher preempt priority (lower priority level) than B and C. B and C have the same preempt priority, but B has a higher subpriority. Interrupts A, B, A, C, B arrive at 1 ms, 3 ms, 7 ms, 10 ms and 12 ms respectively. Each handler takes 5 ms to execute and will also clear the interrupt request. All overheads associated with interrupt processing are assumed to be negligible. What is the total time spent by the processor executing ISR of B in interval [0 ms, 20 ms]? (6 marks)

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started