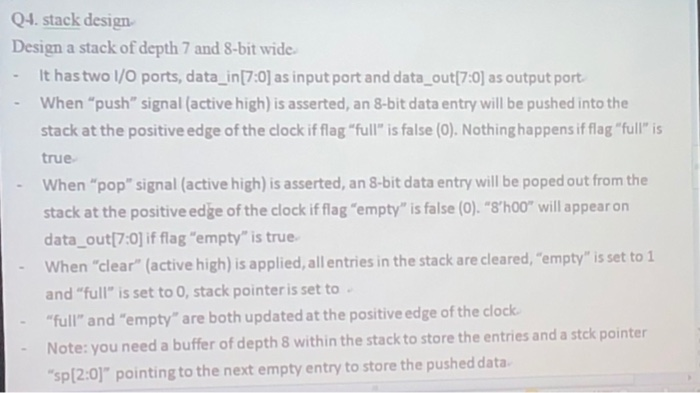

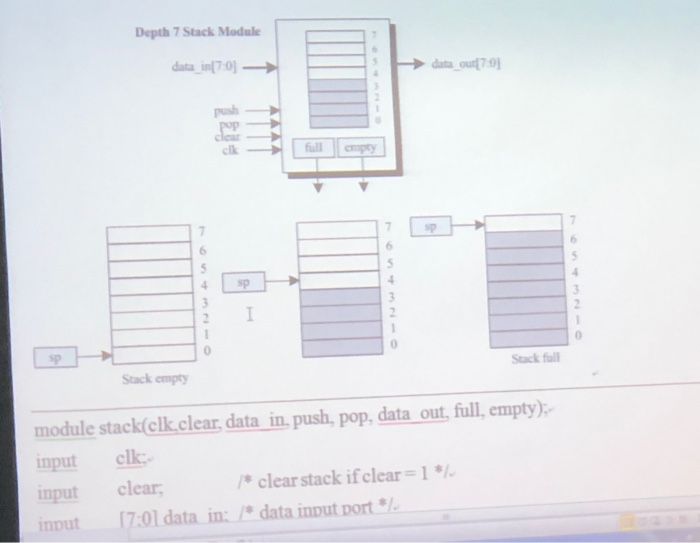

Q4. stack design Design a stack of depth 7 and 8-bit wide It has two l/O ports, data in[7:0 as input port and data out[7:0] as output port When "push" signal (active high) is asserted, an 8-bit data entry will be pushed into the stack at the positive edge of the clock if flag "full" is false (0). Nothinghappens if flag "full is rue When "pop" signal (active high) is asserted, an 8-bit data entry will be poped out from the stack at the positive edge of the clock if flag "empty" is false (0). "8'h00" will appear on data_out 7:0] if flag "empty" is true When "clear" (active high) is applied, all entries in the stack are cleared, "empty" is set to 1 and "full" is set to O, stack pointer is set to full" and "empty" are both updated at the positive edge of the clock Note: you need a buffer of depth 8 within the stack to store the entries and a stck pointer sp[2:0]" pointing to the next empty entry to store the pushed data Depth 7 Stack Module data-in(701 data-out(701 clk | full ||empty 4 sp Stack empty Stack fu module stack(clkclear data in. push, pop, data out, full, empty)- input C input clear input 17:01 data in:/ data input port /* clear stack ifclear-1 * Q4. stack design Design a stack of depth 7 and 8-bit wide It has two l/O ports, data in[7:0 as input port and data out[7:0] as output port When "push" signal (active high) is asserted, an 8-bit data entry will be pushed into the stack at the positive edge of the clock if flag "full" is false (0). Nothinghappens if flag "full is rue When "pop" signal (active high) is asserted, an 8-bit data entry will be poped out from the stack at the positive edge of the clock if flag "empty" is false (0). "8'h00" will appear on data_out 7:0] if flag "empty" is true When "clear" (active high) is applied, all entries in the stack are cleared, "empty" is set to 1 and "full" is set to O, stack pointer is set to full" and "empty" are both updated at the positive edge of the clock Note: you need a buffer of depth 8 within the stack to store the entries and a stck pointer sp[2:0]" pointing to the next empty entry to store the pushed data Depth 7 Stack Module data-in(701 data-out(701 clk | full ||empty 4 sp Stack empty Stack fu module stack(clkclear data in. push, pop, data out, full, empty)- input C input clear input 17:01 data in:/ data input port /* clear stack ifclear-1 *