Answered step by step

Verified Expert Solution

Question

1 Approved Answer

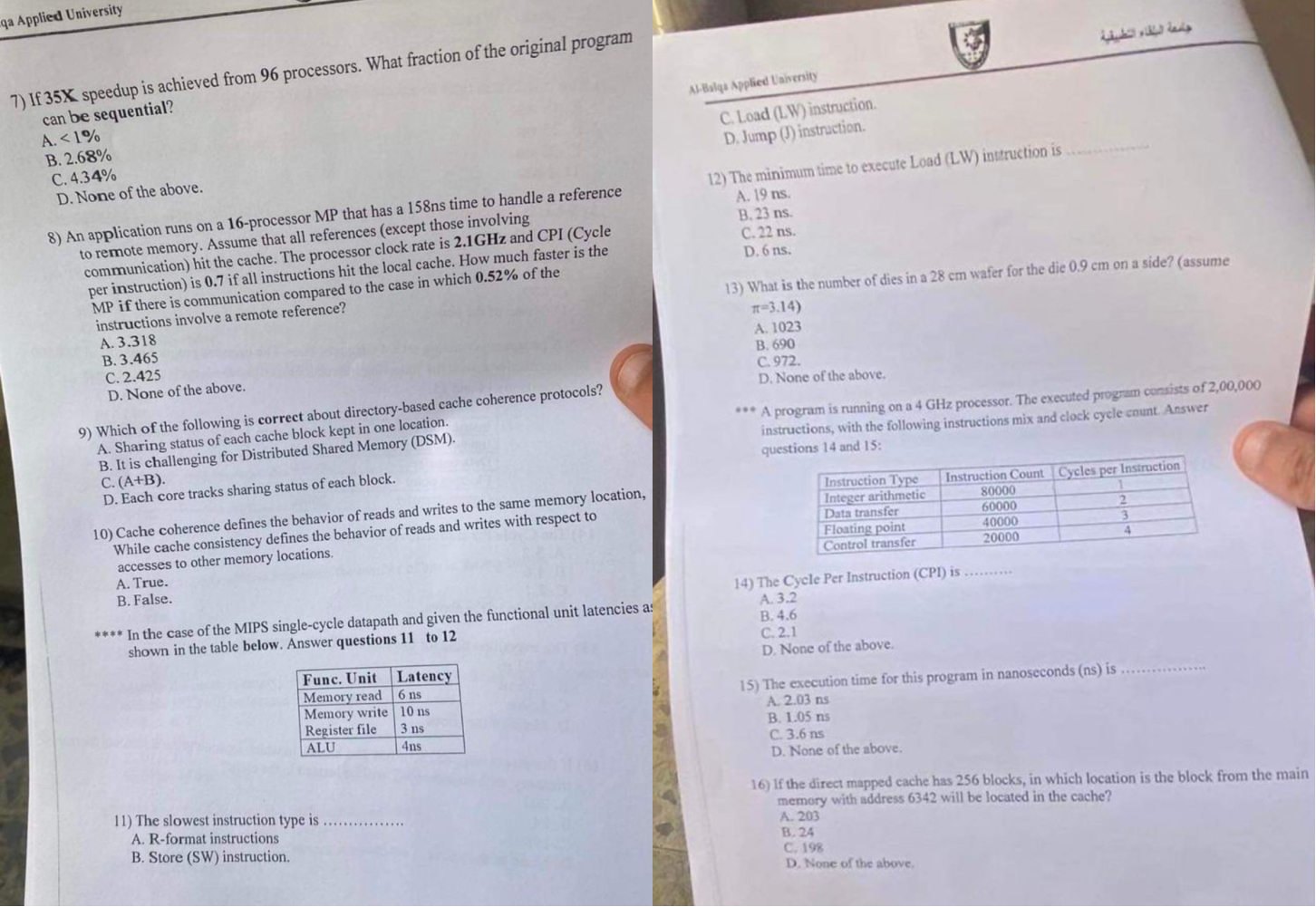

qa Applied University If 3 5 x speedup is achieved from 9 6 processors. What fraction of the original program can be sequential? A .

qa Applied University

If speedup is achieved from processors. What fraction of the original program can be sequential?

A

B

C

D None of the above.

An application runs on a processor MP that has a ns time to handle a reference to remote memory. Assume that all references except those involving communication hit the cache. The processor clock rate is and I Cycle per instruction is if all instructions hit the local cache. How much faster is the MP if there is communication compared to the case in which of the instructions involve a remote reference?

A

B

C

D None of the above.

Which of the following is correct about directorybased cache coherence protocols?

A Sharing status of each cache block kept in one location.

B It is challenging for Distributed Shared Memory DSM

C

D Each core tracks sharing status of each block.

Cache coherence defines the behavior of reads and writes to the same memory location, While cache consistency defines the behavior of reads and writes with respect to accesses to other memory locations.

A True.

B False.

In the case of the MIPS singlecycle datapath and given the functional unit latencies a: shown in the table below. Answer questions to

tableFunc Unit,LatencyMemory read, nsMemory write,

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started