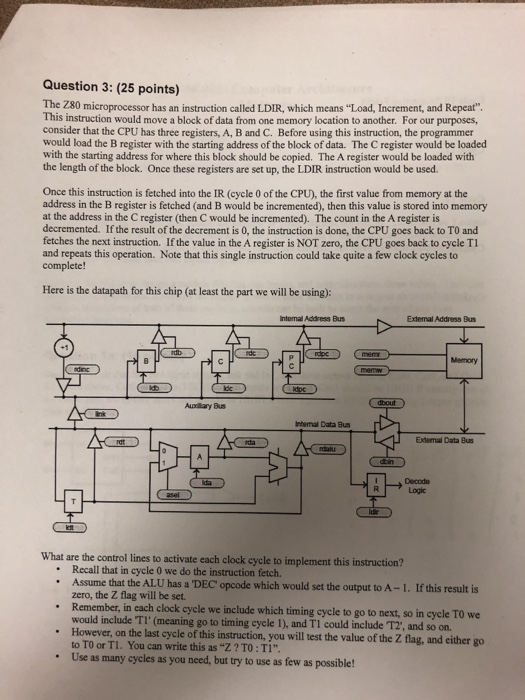

Question 3: (25 points) The Z80 microprocessor has an instruction called LDIR, which means "Load, Increment, and Repeat". is instruction would move a block of data from one memory location to another. For our purposes, consider that the CPU has three registers, A, B and C. Before using this instruction, the programmer would load the B register with the starting address of the block of data. The C register would be loaded with the starting address for where this block should be copied. The A register would be loaded with the length of the block. Once these registers are set up, the LDIR instruction would be used Once this instruction is feched into the IR (cycle 0 of the CPU), the first value from memory at the address in the B register is fetched (and B would be incremented), then this value is stored into memory at the address in the C register (then C would be incremented). The count in the A register is decremented. If the result of the decrement is 0, the instruction is done, the CPU goes back to TO and fetches the next instruction. If the value in the A register is NOT zero, the CPU goes back to cycle TI and repeats this operation. Note that this single instruction could take quite a few clock cycles to complete! Here is the datapath for this chip (at least the part we will be using): nternal Address Bus Extemal Address Bus -1 Memory Internal Data Bus Extemal Data Bus rdalu Decode Logic What are the control lines to activate each clock cycle to implement this instruction? Recall that in cycle 0 we do the instruction fetch. Assume that the ALU has a DEC opcode which would set the output to A-1. If this result is zero, the Z flag will be set. Remember, in each clock cycle we include which timing cycle to go to next, so in cycle TO we would include TI' (meaning go to timing cycle 1), and TI could include T2, and so on. However, on the last cycle of this instruction, you will test the value of the Z flag, and either go to TO or Tl. You can write this as "Z? TO:TI" Use as many cycles as you need, but try to use as few as possible! . Question 3: (25 points) The Z80 microprocessor has an instruction called LDIR, which means "Load, Increment, and Repeat". is instruction would move a block of data from one memory location to another. For our purposes, consider that the CPU has three registers, A, B and C. Before using this instruction, the programmer would load the B register with the starting address of the block of data. The C register would be loaded with the starting address for where this block should be copied. The A register would be loaded with the length of the block. Once these registers are set up, the LDIR instruction would be used Once this instruction is feched into the IR (cycle 0 of the CPU), the first value from memory at the address in the B register is fetched (and B would be incremented), then this value is stored into memory at the address in the C register (then C would be incremented). The count in the A register is decremented. If the result of the decrement is 0, the instruction is done, the CPU goes back to TO and fetches the next instruction. If the value in the A register is NOT zero, the CPU goes back to cycle TI and repeats this operation. Note that this single instruction could take quite a few clock cycles to complete! Here is the datapath for this chip (at least the part we will be using): nternal Address Bus Extemal Address Bus -1 Memory Internal Data Bus Extemal Data Bus rdalu Decode Logic What are the control lines to activate each clock cycle to implement this instruction? Recall that in cycle 0 we do the instruction fetch. Assume that the ALU has a DEC opcode which would set the output to A-1. If this result is zero, the Z flag will be set. Remember, in each clock cycle we include which timing cycle to go to next, so in cycle TO we would include TI' (meaning go to timing cycle 1), and TI could include T2, and so on. However, on the last cycle of this instruction, you will test the value of the Z flag, and either go to TO or Tl. You can write this as "Z? TO:TI" Use as many cycles as you need, but try to use as few as possible